# Marquette University e-Publications@Marquette

Master's Theses (2009 -)

Dissertations, Theses, and Professional Projects

# Computational Modeling of Biological Neural Networks on GPUs: Strategies and Performance

Byron Galbraith Marquette University

#### Recommended Citation

Galbraith, Byron, "Computational Modeling of Biological Neural Networks on GPUs: Strategies and Performance" (2010). *Master's Theses* (2009 -). Paper 61.

http://epublications.marquette.edu/theses\_open/61

# COMPUTATIONAL MODELING OF BIOLOGICAL NEURAL NETWORKS ON GPUS: STRATEGIES AND PERFORMANCE

by

Byron V. Galbraith

A Thesis submitted to the Faculty of the Graduate School,

Marquette University,

in Partial Fulfillment of the Requirements for

the Degree of Master of Science

Milwaukee, Wisconsin

August 2010

#### **ABSTRACT**

#### COMPUTATIONAL MODELING OF BIOLOGICAL NEURAL NETWORKS ON GPUS: STRATEGIES AND PERFORMANCE

Byron V. Galbraith

Marquette University, 2010

Simulating biological neural networks is an important task for computational neuroscientists attempting to model and analyze brain activity and function. As these networks become larger and more complex, the computational power required grows significantly, often requiring the use of supercomputers or compute clusters. An emerging low-cost, highly accessible alternative to many of these resources is the Graphics Processing Unit (GPU) - specialized massively-parallel graphics hardware that has seen increasing use as a general purpose computational accelerator thanks largely due to NVIDIA's CUDA programming interface. We evaluated the relative benefits and limitations of GPU-based tools for large-scale neural network simulation and analysis, first by developing an agent-inspired spiking neural network simulator then by adapting a neural signal decoding algorithm. Under certain network configurations, the simulator was able to outperform an equivalent MPI-based parallel implementation run on a dedicated compute cluster, while the decoding algorithm implementation consistently outperformed its serial counterpart. Additionally, the GPU-based simulator was able to readily visualize network spiking activity in real-time due to the close integration with standard computer graphics APIs. The GPU was shown to provide significant performance benefits under certain circumstances while lagging behind in others. Given the complex nature of these research tasks, a hybrid strategy that combines GPU- and CPU-based approaches provides greater performance than either separately.

#### **ACKNOWLEDGMENTS**

#### Byron V. Galbraith

I would like to thank the following people for their contributions to the completion of this thesis. Craig Struble, my thesis advisor, enabled and supported my research goals while offering invaluable guidance and perspective. Scott Beardsley and Rong Ge, my committee members, provided the opportunities and insights that allowed me to succeed. David Herzfeld provided not only software assistance in the completion of this work, but also friendly competition that encouraged me to work harder.

I would like to extend special thanks to my wife, Karen, for her patience and support during this process.

This research was funded in part by National Science Foundation awards OCI-0923037 and CBET-0521602.

# TABLE OF CONTENTS

|   |       |                                         | iv<br>ii |

|---|-------|-----------------------------------------|----------|

| 1 | Intro | oduction                                | 1        |

|   | 1.1   | Problem Statement                       | 1        |

|   | 1.2   | Thesis Statement                        | 2        |

|   | 1.3   | Contribution                            | 2        |

|   | 1.4   | Organization                            | 3        |

| 2 | Bacl  | kground                                 | 5        |

|   | 2.1   | Graphics Processing Units               | 5        |

|   |       | 2.1.1 GPU Architecture                  | 5        |

|   |       | 2.1.2 General Purpose Computing on GPUs | 7        |

|   |       | 2.1.3 CUDA                              | 9        |

|   |       |                                         | 4        |

|   | 2.2   |                                         | 4        |

|   |       | 2.2.1 The Neuron                        | .5       |

|   |       | 2.2.2 Neural Models                     | 5        |

|   |       |                                         | 6        |

|   |       |                                         | 6        |

|   |       |                                         | 8        |

|   |       |                                         | 9        |

|   | 2.3   | · · · · · · · · · · · · · · · · · · ·   | 20       |

|   |       |                                         | 21       |

|   |       |                                         | 21       |

| 3 | Self- | -Organizing Maps 2                      | 23       |

|   | 3.1   | SOM Algorithm                           | 23       |

|   |       |                                         | 24       |

|   |       | <u> </u>                                | 24       |

|   |       | · · · · · · · · · · · · · · · · · · ·   | 26       |

|   | 3.2   | •                                       | 27       |

|   |       | **                                      | 27       |

|   |       |                                         | 28       |

|   | 3.3   |                                         | 28       |

|   | 3.4   |                                         | 9        |

|    |       | 3.4.1    | Visualization                           | 30  |

|----|-------|----------|-----------------------------------------|-----|

|    | 3.5   | Conclu   |                                         | 31  |

| _  |       |          |                                         |     |

| 4  | -     | _        | ral Networks                            | 34  |

|    | 4.1   |          | approach                                | 35  |

|    |       | 4.1.1    | Data Model                              | 35  |

|    |       | 4.1.2    | Simulation Flow                         | 37  |

|    | 4.2   |          | nance Evaluation                        | 45  |

|    |       | 4.2.1    | Test Environment                        | 47  |

|    | 4.3   |          | 8                                       | 47  |

|    | 4.4   | Discus   | sion                                    | 50  |

|    |       | 4.4.1    | Agent-Inspired Model                    | 51  |

|    |       | 4.4.2    | Validation                              | 53  |

|    |       | 4.4.3    | Visualization                           | 54  |

|    | 4.5   | Conclu   | sion                                    | 55  |

| 5  | Neur  | ral Sign | al Decoding                             | 56  |

|    | 5.1   | _        | Decoding                                | 57  |

|    |       | 5.1.1    | GPU Approach                            | 60  |

|    |       | 5.1.2    | Results                                 | 62  |

|    |       | 5.1.3    | Discussion                              | 65  |

|    | 5.2   | CUSUI    | MMA                                     | 66  |

|    |       | 5.2.1    | Matrix Multiplication                   | 67  |

|    |       | 5.2.2    | The CUSUMMA Algorithm                   | 68  |

|    |       | 5.2.3    | Determining Parameters                  | 69  |

|    |       | 5.2.4    | Special Cases                           | 72  |

|    |       | 5.2.5    | Performance Results                     | 73  |

|    |       | 5.2.6    | Discussion                              | 76  |

| 6  | Conc  | clusions | And Future Work                         | 77  |

| DI | DI IA | GRAPI    | uv                                      | 79  |

| DI | bLIO  | GKALI    |                                         | 19  |

| A  | CUD   | A Hello  | World Code Listing                      | 83  |

| В  | SOM   | I Visual | ization Code Listings                   | 85  |

| C  | Spik  | ing Neu  | ral Network Visualization Code Listings | 93  |

| D  | Neur  | al Deco  | oding Code Listings                     | 115 |

# LIST OF FIGURES

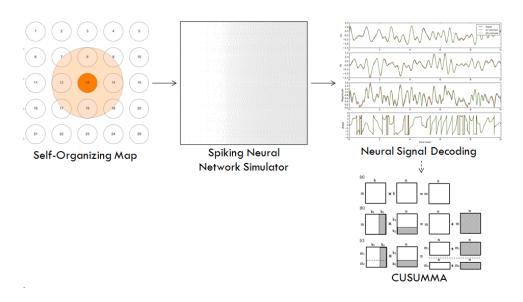

| 1.1 | Organization of research contributions described in this thesis                                                                                                                                                                                                                                                                                                                   | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

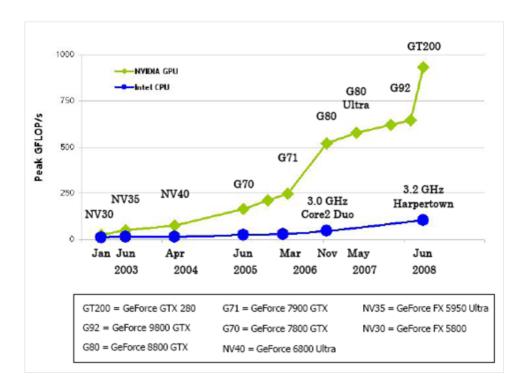

| 2.1 | Comparison of peak GFLOPS for NVIDIA GPUs and Intel CPUs [46]                                                                                                                                                                                                                                                                                                                     | 6  |

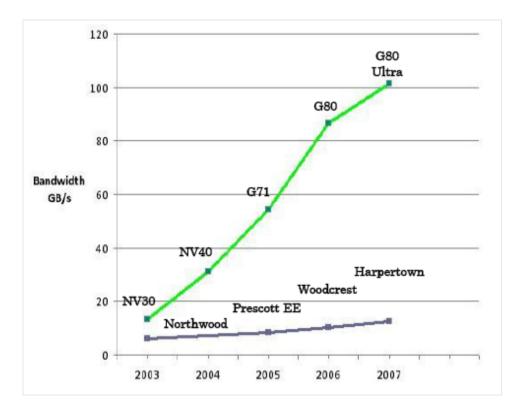

| 2.2 | Comparison of peak DRAM bandwidth for NVIDIA GPUs and Intel CPUs [46].                                                                                                                                                                                                                                                                                                            | 7  |

| 2.3 | Relative devotion of transistors in a 4-core CPU vs. 128-core GPU [46]                                                                                                                                                                                                                                                                                                            | 7  |

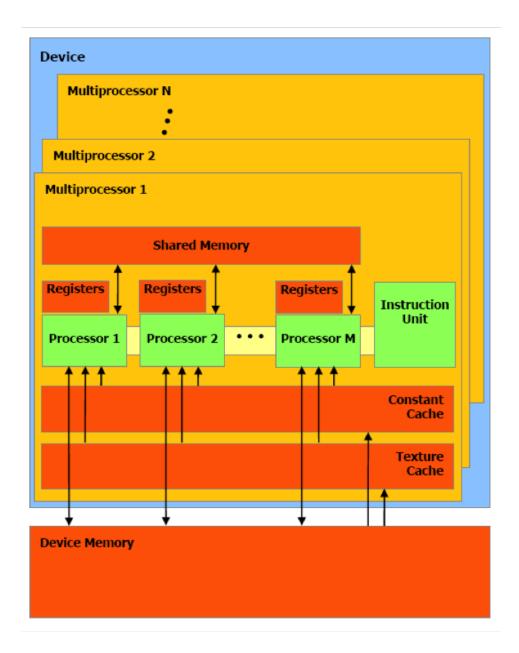

| 2.4 | Layout schematic for the NVIDIA G80 GPU architecture [46]                                                                                                                                                                                                                                                                                                                         | 8  |

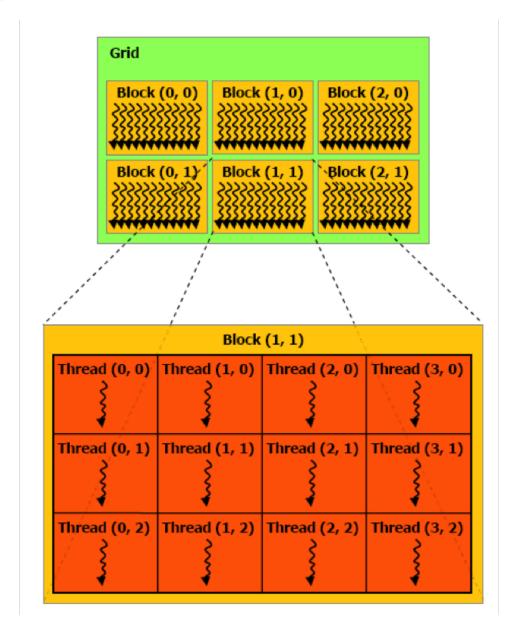

| 2.5 | Illustration depicting the two-tier CUDA thread hierarchy [46]                                                                                                                                                                                                                                                                                                                    | 10 |

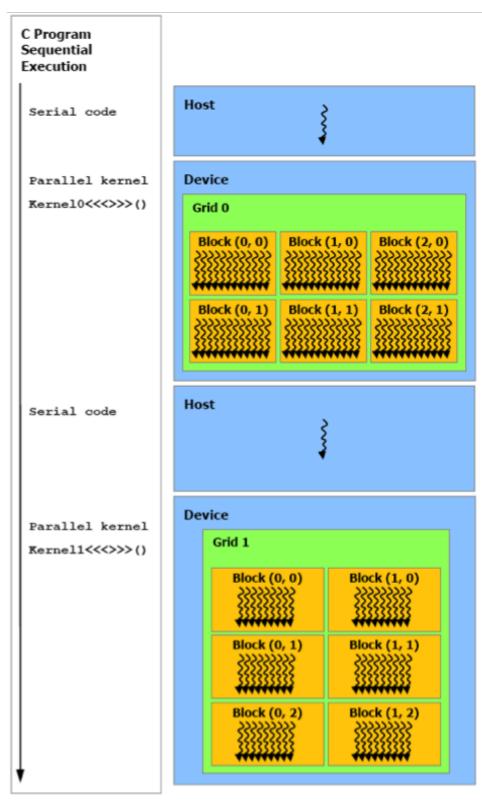

| 2.6 | Typical CUDA program switches between serial host (CPU) and parallel device                                                                                                                                                                                                                                                                                                       |    |

|     | (GPU) execution [46]                                                                                                                                                                                                                                                                                                                                                              | 12 |

| 2.7 | Results of querying a GeForce GTX 260 (GT200 series) GPU                                                                                                                                                                                                                                                                                                                          | 13 |

| 2.8 | Results of querying a GeForce 8200 (G80 series) GPU                                                                                                                                                                                                                                                                                                                               | 13 |

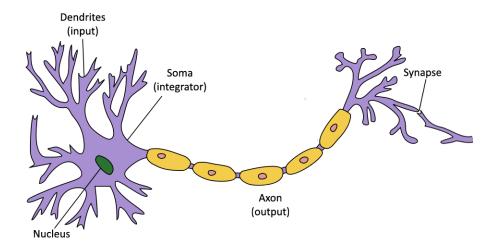

| 2.9 | The key components of a neuron. Signals in the form of ionic currents travel from the dendrites to the soma, increasing the cell membrane potential. If the soma reaches threshold, an action potential is generated and sent down the axon. The action potential event is relayed to the connecting neuron at the synapse. Image modified from [35]. Licensed under CC-BY-SA-3.0 | 16 |

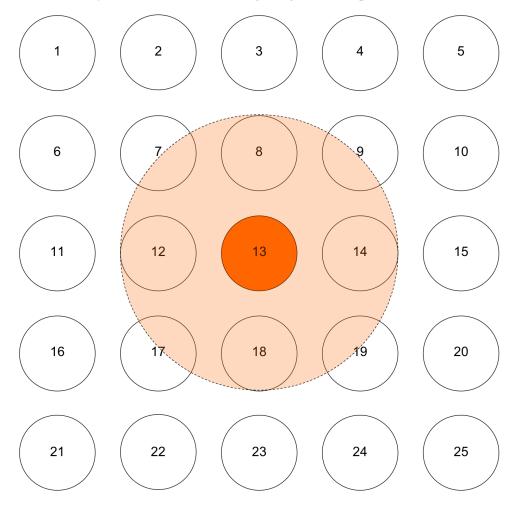

| 3.1 | A 25 neuron SOM configured in a 5x5 grid. The orange neuron represents the BMU, while the shaded area around it is the neighborhood of effect                                                                                                                                                                                                                                     | 25 |

| 3.2 | 2400 x 1800 pixel bitmap image [47] used as the input data source. Licensed under CC-BY-NC-2.0                                                                                                                                                                                                                                                                                    | 29 |

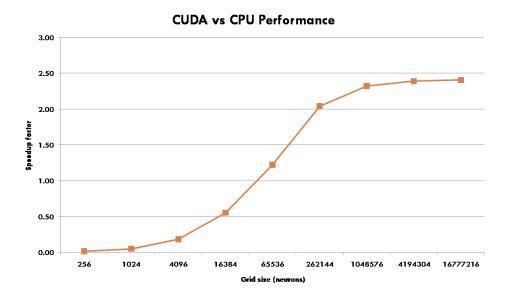

| 3.3 | Performance of the GPU version versus the CPU version of SOM training for a single iteration. Speedup is defined as GPU/CPU                                                                                                                                                                                                                                                       | 30 |

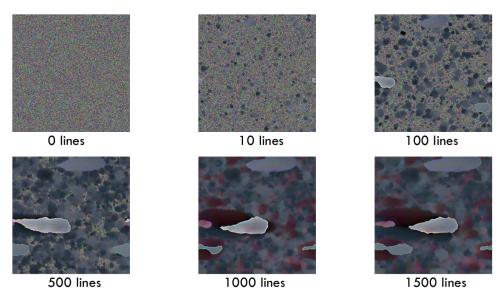

| 3.4 | State of the SOM as rendered by a bitmap image at various stages in training. One line = 1800 inputs                                                                                                                                                                                                                                                                              | 31 |

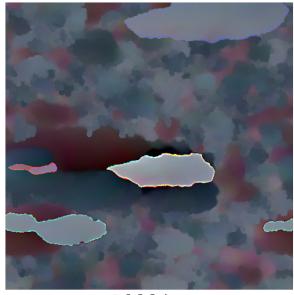

| 3.5 | Final state of the SOM after all pixels had been presented                                                                                                                                                                                                                                                                                                                        | 32 |

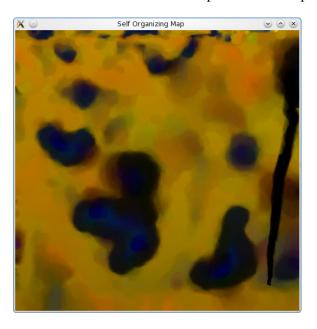

| 3.6 | A screen capture of an OpenGL application depicting the training of a SOM in real time. The source input used was related to Marquette University, thus the emergence                                                                                                                                                                                                             |    |

|     | of gold and blue.                                                                                                                                                                                                                                                                                                                                                                 | 32 |

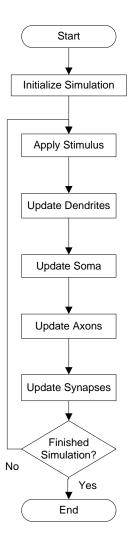

| 4.1 | The general recurrent network simulation starts with an initialization phase followed<br>by the actual simulation loop and a series of five update processes that together<br>handle a single time step. This loop runs until either all specified time steps have                                                                                                                |    |

|     | completed or the user ends the simulation                                                                                                                                                                                                                                                                                                                                         | 38 |

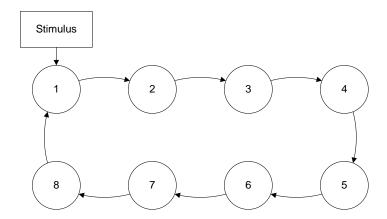

| 4.2  | Simple schematic of an eight-neuron recurrent network in a ring topology. In this particular configuration, an additional external stimulus is applied to the first neuron                                                                                                              |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4.3  | in order to initiate network activity                                                                                                                                                                                                                                                   |  |

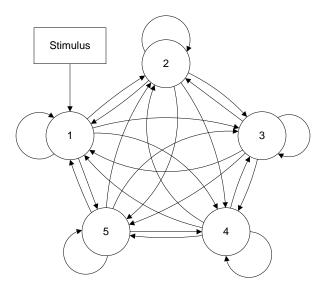

|      | ery other neuron in addition to a connection with itself for a total of 25 connections. In this particular configuration, an additional external stimulus is applied to the first neuron in order to initiate network activity                                                          |  |

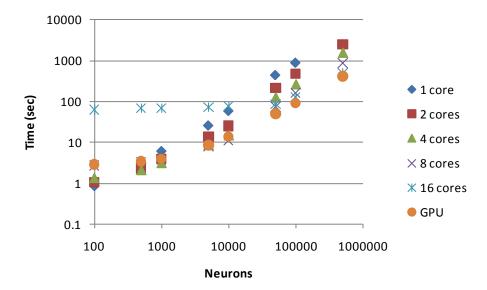

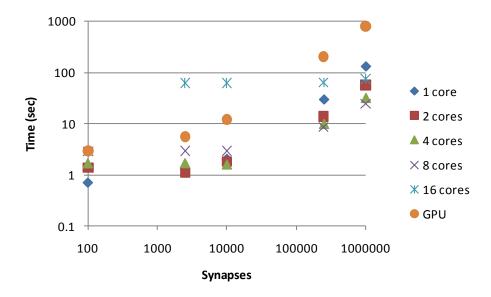

| 4.4  | Time needed to complete a simulation for a neural population in a ring topology.  The number of synapses equals the number of neurons                                                                                                                                                   |  |

| 4.5  | Time needed to complete a simulation for a fully connected neural population. The number of neurons equals the square root of the number of synapses                                                                                                                                    |  |

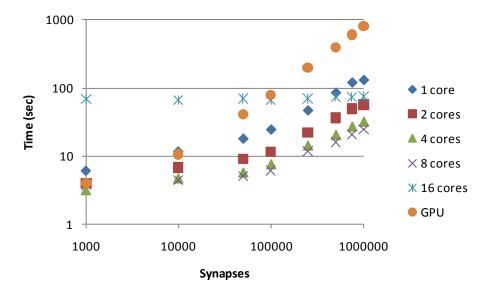

| 4.6  | Time needed to complete a simulation for a 1000 neuron population. The percentage of connectivity ranges from $0.1\%$ at $1000$ synapses to $100\%$ at 1 million synapses                                                                                                               |  |

| 4.7  | Time needed to complete a simulation for neural populations containing 500,000 synapses. The percentage of connectivity ranges from 50% at 1000 neurons to 0.0002% at 500,000 neurons                                                                                                   |  |

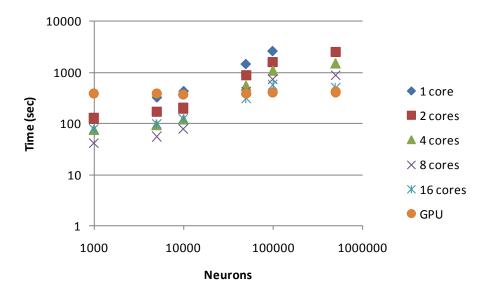

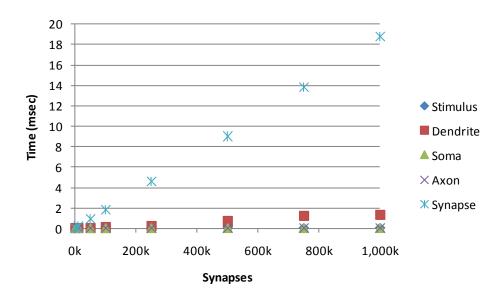

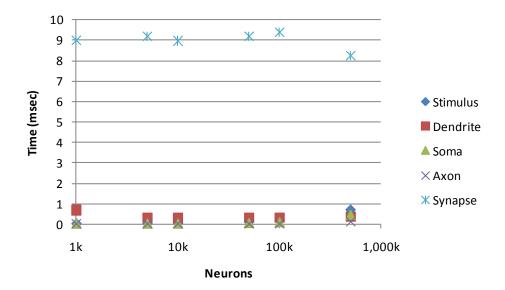

| 4.8  | Average time (n=40,000) needed to complete the individual GPU kernels for a 1000 neuron population. The percentage of connectivity ranges from $0.1\%$ at $1000$                                                                                                                        |  |

| 4.9  | synapses to 100% at 1 million synapses                                                                                                                                                                                                                                                  |  |

| 4.10 | from 50% at 1000 neurons to 0.0002% at 500,000 neurons                                                                                                                                                                                                                                  |  |

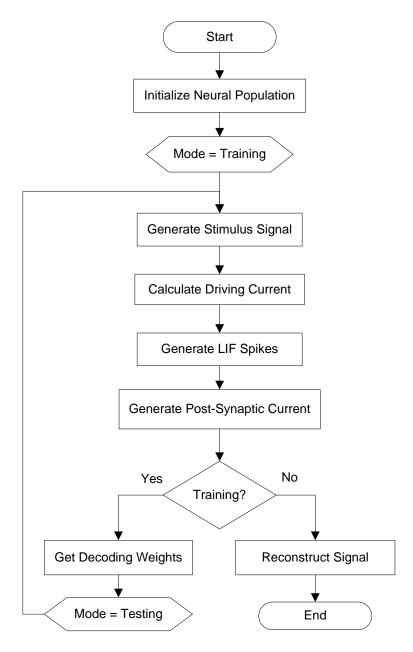

| 5.1  | Simulation flow for the PT decoding trials. At the PSC generation, decoding weight determination, and signal reconstruction operations, both SU and MU results are calculated                                                                                                           |  |

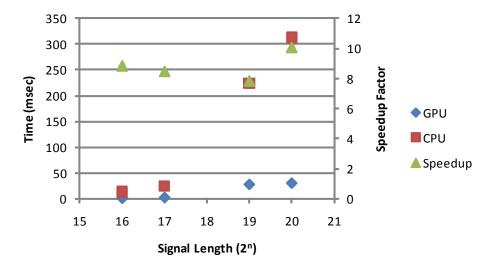

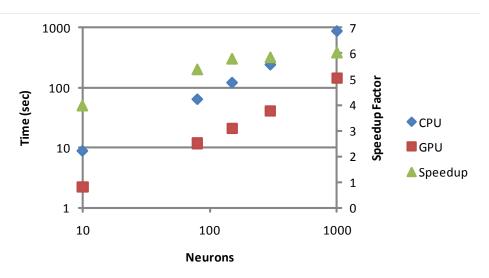

| 5.2  | Performance of the GPU (CUFFT) vs. the CPU (FFTW) convolution routines for signal lengths of a given power of 2. Speedup is equal to $CPU/GPU$                                                                                                                                          |  |

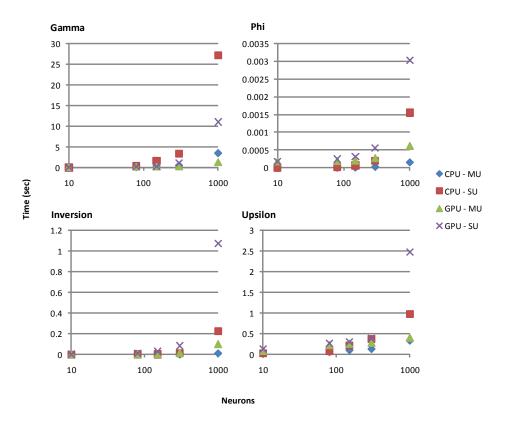

| 5.3  | Performance comparison breakdown among the various components of the optimal decoding weight calculation process                                                                                                                                                                        |  |

| 5.4  | Sum of the four component times making up the process to find the optimal decoding weights                                                                                                                                                                                              |  |

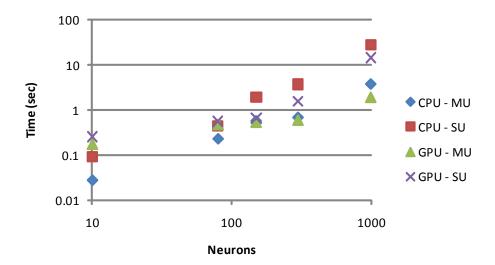

| 5.5  | Performance of the GPU-enabled version of the simulation vs the CPU-only version. Speedup is defined as $CPU/GPU$                                                                                                                                                                       |  |

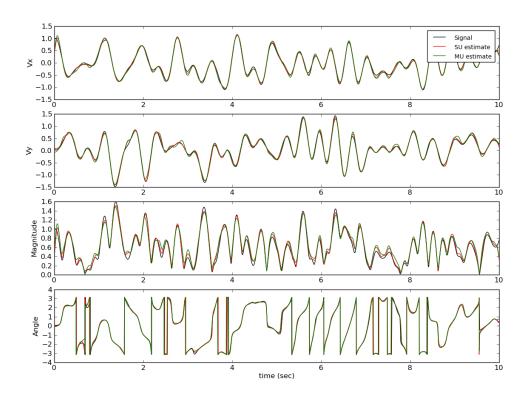

| 5.6  | Signal reconstruction accuracy of the GPU-enabled version of the decoding algorithm. From the top, the charts depict the $x$ and $y$ components, the magnitude, and the angle of the 2D input signal (black) over time compared to the SU (red) and MU (green) reconstructed estimates. |  |

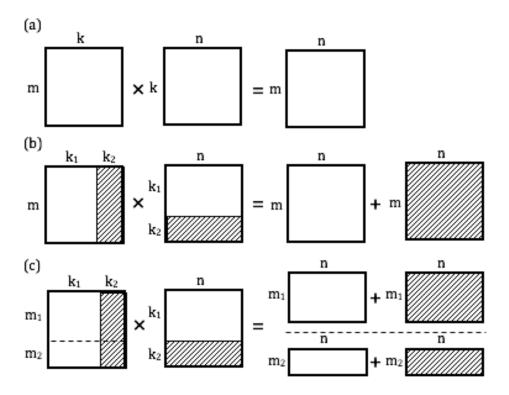

| 5.7  | Partitioning strategies for $A*B=C$ - (a) no partitioning, (b) partitioning by shared dimension $k$ , and (c) partitioning by leading dimension $m$ of $A$ and shared                                                                                                                   |  |

|      | dimension $k$ .                                                                                                                                                                                                                                                                         |  |

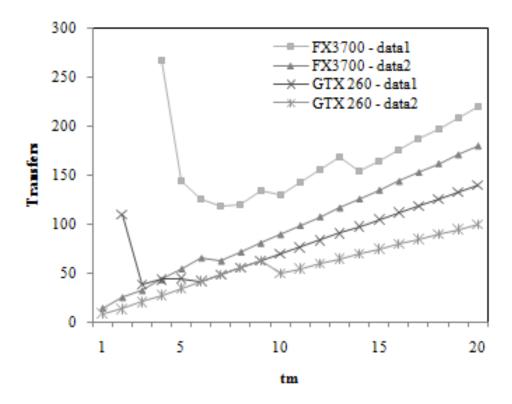

| 5.8  | Iterative Solver - data1 is $m = n = k = 20$ k while data2 is $m = n = 1$ k, $k = 400$ k. |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | Both sets have the same number of elements in the input but drastically different         |    |

|      | output space requirements. Missing values indicate the parameter configuration is         |    |

|      | invalid                                                                                   | 74 |

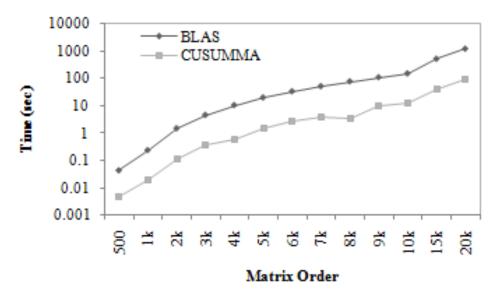

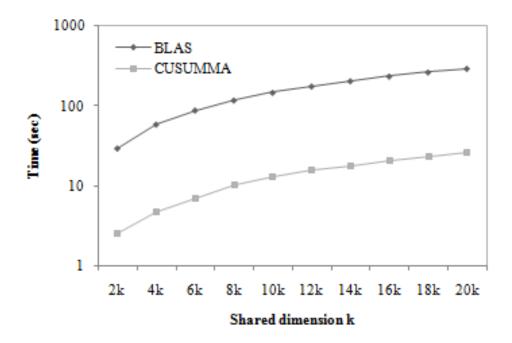

| 5.9  | Performance of CUSUMMA vs. BLAS for square matrices                                       | 75 |

| 5.10 | Performance of CUSUMMA vs. BLAS for rectangular matrices ( $m = n = 10$ k).               | 76 |

|      |                                                                                           |    |

# LIST OF TABLES

| 4.1 | Data structures used in the execution of the agent-based GPU model            | 36 |

|-----|-------------------------------------------------------------------------------|----|

| 4.2 | Memory requirements (in bytes) for data elements stored on the GPU. As $S >>$ |    |

|     | N and $pscFilterSize$ is typically between 50 and 200, the number of synapses |    |

|     | dominate the memory requirements                                              | 37 |

#### CHAPTER 1

#### Introduction

#### 1.1 Problem Statement

Artificial neural networks are a class of computational tools used in such fields as pattern recognition, machine learning, and knowledge discovery. They are inspired from the emergent properties of actual neurons found in the human brain where several small independent units acting in unison can give rise to complex functionality. One classic example is the self-organizing map, a network of artificial neurons that, when trained, can be used to discover novel relationships between multidimensional data sets. The training process can be very slow dependent on the data set which may prohibit use, so developing methods to speed up training can enable larger and more complex data sets to be analyzed.

Modeling actual biological neural networks is also of significant importance in the fields of computational neuroscience and robotics. By simulating networks of biologically-based neurons, researchers hope to gain deeper understanding of brain activity and function as well as develop control devices that can mimic the brain's own fine motor control ability. As these networks become larger and more complex, the computational power required grows significantly, often requiring the use of supercomputers or compute clusters. As such, many researchers are unable to achieve the level of granularity or network complexity desired, thus inhibiting or halting progress.

An emerging low-cost, highly accessible alternative to many of these resources is the Graphics Processing Unit (GPU) - specialized massively-parallel graphics hardware that has seen increasing use as a general purpose computational accelerator thanks largely due to NVIDIA's CUDA programming interface. Scientific and clinical applications that benefit from parallelization,

such as in fluid dynamics, bioinformatics, and medical image analysis, can gain significant speedup just by adapting exiting strategies to incorporate GPU acceleration. As NVIDIA continues to invest heavily in research and marketing for advancing the GPU as a general computational tool, the GPU is an intriguing platform to target development efforts for scientific applications.

Adapting large-scale biologically-inspired neural networks to utilize GPUs is especially attractive as these classes of problems consume significant computational resources. These enhanced simulations could lead to greater understanding of neural function resulting in improved prosthetic and rehabilitation devices for patients. As GPUs are orders of magnitude cheaper than supercomputers or large compute clusters, GPU-based tools for large-scale neural simulations enable a larger pool of researchers to study these problems. However, utilizing GPUs as computational accelerators is not without drawbacks and challenges. There exists a need for solid understanding of what the GPU is able to offer the field of neural simulation as well as sound strategies for incorporating GPUs into existing and future models and tools.

#### 1.2 Thesis Statement

Computational models of biological neural networks can be efficiently implemented on GPUs.

#### 1.3 Contribution

The design and implementation of GPU-enabled neural network modeling tools using the CUDA platform are provided in this thesis. They were developed as follows (Figure 1.1).

- A self-organizing map implementation demonstrates the trade-offs between different arrangements of mapping threads to neurons, the inherent barrier of simulation time step, and a glimpse into concurrent network training and visualization.

- An agent-inspired spiking neural network simulation tool is designed and implemented, taking advantage of the massively parallel nature of the GPU to mimic neural behavior. The beginning of a GPU-enhanced neural network simulation tool focused on biological constraints and modalities is presented in detail.

- A neural signal decoding algorithm is successfully adapted to use the GPU as a computational accelerator for finding effective linear filter decoder weights.

- As part of the neural decoding algorithm implementation, the CUSUMMA algorithm was created to perform general matrix-matrix multiplications portably and dynamically on any CUDA-enabled GPU.

Figure 1.1: Organization of research contributions described in this thesis.

## 1.4 Organization

The rest of this thesis is arranged as follows. Chapter 2 provides background information relating to NVIDIA's GPU architecture, the CUDA programming model, basic neural physiology, modeling biological neural networks, and neural network simulation. The next three chapters present the creation and evaluation of GPU-based neural network modeling and analysis tools with focus on performance versus non-GPU implementations. Chapter 3 describes the performance of a self-organizing map implementation on a GPU with additional focus on the ability to visualize the network as it trains in real-time. Chapter 4 describes a GPU-based agent-inspired spiking neural network simulator. The design and implementation of this tool are detailed along with performance results compared to an MPI version and another look at visualizing real-time network activity. In Chapter 5, a neural signal decoding algorithm is adapted to use a GPU for acceleration of linear

algebra and convolution operations in order to speed up the decoding process. Concluding remarks are made in Chapter 6, where commentary on the overall success of GPU-adapted neural population simulations is offered and areas for further development are considered. Finally, several appendices provide complete code listings for some of the GPU code developed.

#### **CHAPTER 2**

### Background

The work contained herein relies heavily on two key technologies: computational acceleration using graphics processing units; and the modeling and simulation of biologically-based neural networks. This chapter provides an overview of these concepts with emphasis on the specific tools employed.

# 2.1 Graphics Processing Units

A graphics processing unit (GPU) is a specialized piece of computer hardware optimized for the processing and rendering of 3D computer graphics. As this process is largely data-parallel, modern GPUs have been designed to be massively parallel processors that are highly efficient at performing billions of floating point operations per second (Figure 2.1). In order to accomplish this feat, GPU hardware designers departed from traditional CPU architecture.

#### 2.1.1 GPU Architecture

At the time of writing, modern CPU's contain up to six processing cores. Each core is a general purpose processing element that supports a wide variety of instructions, while memory access is multi-tiered, employing several layers of caching. On the other hand, GPUs — specifically those produced by NVIDIA — dedicate their silicon to several multiprocessors, each containing many single-precision processing elements with limited caching and flow control. Since caching is not as important as arithmetic for graphics operations, emphasis was instead placed on increasing the memory bandwidth to the GPU's DRAM (Figure 2.2). In comparison to the six

Figure 2.1: Comparison of peak GFLOPS for NVIDIA GPUs and Intel CPUs [46].

cores of a current high-end CPU, a high-end GPU has 240 cores, and, unlike the limited single or double thread concurrency model of current CPUs, the GPU can manage and efficiently schedule hundreds of thousands of light-weight threads across its cores. Figure 2.3 provides a simple schematic representing the differences in general architectures between the two platforms.

Looking closer at the NVIDIA GPU architecture (Figure 2.4), it is seen to be made up of a number of *multiprocessors*. In current architectures, each multiprocessor contains eight single-precision floating point operation processing elements with a shared instruction unit. Not shown here is the single double-precision processing unit also present on newer NVIDIA GPUs. There are registers for each of the processors used to handle per-thread memory requirements, as well as a slightly slower shared memory buffer that allows threads on the same multiprocessor to communicate. Additionally, each multiprocessor has a limited amount of read-only cache for constant parameters and texture data. In all cases but the registers, the programmer must make explicit use of of these other memories. Finally, there is the GPU DRAM or device memory that any thread can access. All in all there are 8kb or 16kb total registers, 16kb shared memory, and 64kb constant memory per multiprocessor, while the amount of DRAM can range from 256Mb in

Figure 2.2: Comparison of peak DRAM bandwidth for NVIDIA GPUs and Intel CPUs [46].

Figure 2.3: Relative devotion of transistors in a 4-core CPU vs. 128-core GPU [46].

low end and laptop GPUs to 4Gb in dedicated compute devices. Texture memory is slightly different, in that the texture data is stored in DRAM, but must be specially defined at compile time in order to achieve the performance benefits due to caching.

#### 2.1.2 General Purpose Computing on GPUs

While parallelization libraries such as MPI [28] and OpenMP [15] allow developers to utilize each core simultaneously, the generation of these threads is computationally expensive.

Figure 2.4: Layout schematic for the NVIDIA G80 GPU architecture [46].

Additionally, the number of concurrently active threads is limited to the number of cores available. Attempting to provision more threads than cores can cause performance degradation as threads must wait until cores become available. It seems natural then that researchers would want to harness the highly optimized, massively parallel GPU for non-graphics applications. Early efforts to do so were termed *General Purpose Computing on GPUs (GPGPU)* and were met with significant challenges. Until the introduction of NVIDIA's CUDA (Section 2.1.3) in 2006, the only option for GPGPU was to reformulate the scientific problem into OpenGL or DirectX, low-level

graphics APIs (Application Programming Interface) that did not support many of the common constructs found in general purpose programming languages. As this required both a mastery of the graphics APIs as well as a thorough understanding of the application being ported, very few people were successful.

#### 2.1.3 CUDA

In its G80 class of GPUs, NVIDIA dedicated extra silicon to a programmable interface that allowed developers to use the GPU as a general purpose stream processor. *Stream processing* is related to the SIMD (Single Instruction Multiple Data) programming paradigm where a single kernel function is applied to multiple data elements in parallel. Unlike SIMD, NVIDIA's CUDA (Compute Unified Device Architecture) does not guarantee explicit synchronization or execution order between processing elements. They call their model SIMT (Single Instruction Multiple Thread) as the *thread* is the basic processing element from the programmer's perspective.

#### **Thread Model**

The CUDA SIMT paradigm achieves massive parallelism through the scheduling and execution of hundreds to millions of threads. As this number of threads greatly exceeds the number of physical processing elements, the threads are arranged into a two-tiered structure to facilitate scheduling. The basic unit of organization is a *thread block* (Figure 2.5 bottom), a 3D array of no more than 512 threads with the maximum allowable dimensions in the x, y, and z coordinates being 512, 512, and 64, respectively. The thread scheduler will physically keep a thread block together by assigning it to an available multiprocessor. Thread blocks are in turn organized into a 2D array called a *thread grid* (Figure 2.5 top), which has maximum allowable dimensions of 65535 x 65535. All thread blocks in a grid share the same dimensions. As only one thread grid can be specified per kernel launch, the maximum number of threads that can be requested at a time is 2.2 trillion.

Whether requesting 2.2 trillion threads or just one, the actual execution of threads occurs in 32-thread bundles called *warps*. A warp executes in SIMD fashion, so all 32 threads execute simultaneously and finish at the same time. A multiprocessor can execute up to 24 or 32 warps at any given time for a total of 768 or 1024 threads. Since a thread block is limited to 512 threads, it

is possible for multiple blocks to occupy a single multiprocessor. Thread blocks cannot share processing elements, however, so the maximum number of thread blocks per multiprocessor is eight.

Figure 2.5: Illustration depicting the two-tier CUDA thread hierarchy [46].

#### **Programming Model**

One of the attractive features of CUDA for GPGPU is the programming API provided by NVIDIA. Instead of having to deal with low-level graphics APIs, NVIDIA added a few key

extensions to ANSI C, allowing programmers to use a familiar environment to create GPU-based applications which could then be compiled using the provided *nvcc* compiler. This tool is actually a wrapper around GCC on the Linux and Mac OS X platforms and the Visual C++ compiler on the Windows platform. In addition to processing the CUDA-specific extensions, it generates the PTX assembly code used by the GPU for device specific kernels and functions, while passing the standard C/C++ code on to the respective local compiler.

The GPU is incapable of handling general program flow by itself, so every CUDA program is a CPU, or *host*, application that must explicitly invoke kernel execution and data transfer to and from the GPU, or *device*. Typical execution flow is depicted in Figure 2.6, where a serial process sets up the application state and prepares data for processing before launching a kernel with a defined thread grid. It's important to note that kernel launching is asynchronous, so control immediately returns to the host process without waiting for all the kernel threads to finish. Certain operations, such as copying data from the device back to the host, block until all threads have completed execution.

Serial code executes on the host while parallel code executes on the device.

Figure 2.6: Typical CUDA program switches between serial host (CPU) and parallel device (GPU) execution [46].

CUDA supports multiple GPUs if present, though the programmer has to manually switch contexts between GPUs as part of the application. The programmer can also decide which GPU to use at runtime based on the reported compute capabilities. Examples of device query output can be seen for a GeForce GTX 260 (Figure 2.7) and a GeForce 8200 (Fig. 2.8).

```

vice 0: "GeForce GTX 260"

CUDA Driver Version:

CUDA Runtime Version:

2.30

CUDA Capability Major revision number:

CUDA Capability Minor revision number:

939327488 bytes

Total amount of global memory:

Number of multiprocessors:

Number of cores:

216

65536 bytes

Total amount of constant memory:

Total amount of shared memory per block:

16384 bytes

Total number of registers available per block: 16384

Warp size:

Maximum number of threads per block:

512

Maximum sizes of each dimension of a block:

512 x 512 x 64

Maximum sizes of each dimension of a grid:

65535 x 65535 x 1

Maximum memory pitch:

2147483647 bytes

Texture alignment:

256 bytes

1.35 GHz

Clock rate:

Concurrent copy and execution:

Yes

Run time limit on kernels:

No

Integrated:

No

Support host page-locked memory mapping:

Yes

Compute mode:

Default (multiple host threads can use

this device simultaneously)

```

Figure 2.7: Results of querying a GeForce GTX 260 (GT200 series) GPU.

```

evice 1: "GeForce 8200

CUDA Driver Version:

3.0

CUDA Runtime Version:

2.30

CUDA Capability Major revision number:

CUDA Capability Minor revision number:

Total amount of global memory:

265617408 bytes

Number of multiprocessors:

Number of cores:

Total amount of constant memory:

65536 bytes

16384 bytes

Total amount of shared memory per block:

Total number of registers available per block: 8192

Warp size:

32

Maximum number of threads per block:

Maximum sizes of each dimension of a block:

512 x 512 x 64

Maximum sizes of each dimension of a grid:

65535 x 65535 x 1

2147483647 bytes

Maximum memory pitch:

Texture alignment:

256 bytes

Clock rate:

1.20 GHz

Concurrent copy and execution:

Run time limit on kernels:

No

Integrated:

Yes

Support host page-locked memory mapping:

Yes

Compute mode:

Default (multiple host threads can use

this device simultaneously)

```

Figure 2.8: Results of querying a GeForce 8200 (G80 series) GPU.

For a simple Hello World example CUDA program, see Listing A.1. A more in-depth presentation of CUDA can can be found in NVIDIA's <u>CUDA Programming Guide</u> [46], while the textbook <u>Programming Massively Parallel Processors: A Hands-on Approach</u>, by Kirk and Hwu, provides a solid introduction to CUDA programming with exercises and case studies [37].

#### Libraries

Along with the standard Runtime API to CUDA, NVIDIA also provides a Driver API. The main difference is that the Driver API requires more context initialization for kernel launches with the potential for increased performance. It also supports Just-In-Time (JIT) compilation of kernels, allowing developers to invoke dynamic kernel functions from other environments, such as Java [1] and Python [38]. At a much higher level, NVIDIA also includes the CUFFT [45] and CUBLAS [44] libraries as standalone tools for GPU-enhanced FFT and linear algebra operations. These require even less expertise on the programmer's part as the interfaces are designed to mimic the FFTW [23] and BLAS [9] routine calls, enabling them to be dropped in-place to existing code with minimal changes required.

#### 2.1.4 OpenCL

Worth briefly mentioning, OpenCL [42] is a standardized language overseen by the Khronos Group (of OpenGL fame) for harnessing a variety of computational accelerators including GPUs, IBM's Cell Broadband Engine, digital signal processors, and other special purpose hardware. The first draft specification was released in 2009, with vendor driver implementations following shortly thereafter. As CUDA is specific to NVIDIA GPUs, OpenCL offers a platform-independent alternative to developing GPU applications. However, OpenCL has adopted many of the extensions introduced by CUDA into its programming model, so transitioning from CUDA to OpenCL should be fairly straightforward if so desired.

## 2.2 Modeling Neural Networks

The animal nervous system consists of a complex network of intercommunicating cells called *neurons*. The number of neurons in an organism can range from a handful in invertebrates

up to the tens of billions found in the human brain. Attempting to understand and model how neural behavior gives rise to the phenomena of cognition, perception, and memory is a subject that has driven researchers for decades.

#### 2.2.1 The Neuron

A neuron consists of three main components: the cell body, or *soma*, the *dendrites*, and the *axon*. In engineering terms, the dendrites handle the input, the soma integrates the signals coming from the dendrites, and the axon transmits any output signal (Figure 2.9). While certain neurons transduce environmental information or deliver control signals to other tissues such as muscle, the large majority of neurons communicate with other neurons. This neural communication occurs via chemo-electrical signaling in the form of modulated cell membrane potentials. Some neurons use graded changes in potential to communicate information, while most use a series of sharp, rapid changes called *action potentials*, or spikes. These spikes are generated at the soma and travel down the axon to the axon terminal, where the sudden change in potential causes the release of neurotransmitter molecules into the space between neurons called the *synapse*. These molecules bind to receptors in the afferent neuron's dendrites resulting in a *post-synaptic current (PSC)* that represents the input to that neuron. Through adaptive addition and subtraction of the dendrite receptors, effective weighting of the inputs from various neurons is achieved.

For an excellent resource on neurons and neural physiology, see Principles of Neural Science, by Kandel, Schwartz, and Jessell [36].

#### 2.2.2 Neural Models

The level of complexity undertaken in modeling neurons is almost entirely dependent on the type of question the modeler is asking. For instance, if simple spiking behavior is of interest, then all that is needed from a model is a way to aggregate inputs and emit spikes over time thus allowing for the neuron to be treated largely as a mathematical construct. For more in-depth studies of intra-cell behavior, this simple representation is insufficient, so morphological elements such as ion channels and the 3D structure of the cell are incorporated. In general, the researcher

Figure 2.9: The key components of a neuron. Signals in the form of ionic currents travel from the dendrites to the soma, increasing the cell membrane potential. If the soma reaches threshold, an action potential is generated and sent down the axon. The action potential event is relayed to the connecting neuron at the synapse. Image modified from [35]. Licensed under CC-BY-SA-3.0.

typically needs to identify the models for neural morphology, dynamics, and communication, as well as the framework in which to evaluate neural response.

#### 2.2.3 Neural Morphology

The representation of neuron morphology is divided into either single or multiple compartment models. Single compartment models, or *point neurons*, treat the entire neuron as a single entity from a system state perspective. For instance, while cell membrane potential will differ across the body of a real neuron depending on the structure and location, a point neuron assumes the membrane potential is uniform. All the neural models in this work are point neurons. Multi-compartment models, on the other hand, break the neuron into individual sections, with the number and shape of each compartment dependent on the type of neuron being modeled and the level of granularity required.

#### 2.2.4 Neural Dynamics

The way a neuron responds to the change in input current over time is expressed in its dynamical behavior model. There exist several models for neural spiking dynamics, each with their own strengths and weaknesses. Three of the common classes of models are described below.

#### **Leaky Integrate-and-Fire**

The *Leaky Integrate-and-Fire (LIF)* neuron model [2] is one of the oldest and most basic representations of neural activity. It is computationally straightforward, consisting of the single differential equation

$$\frac{dV(t)}{dt} = -\frac{1}{\tau^{RC}}(V(t) - J_M(t)R),$$

(2.1)

where V(t) is the membrane voltage at time t,  $\tau^{RC}$  is the RC time constant, R is the leak resistance, C is the capacitance of the cell membrane, and  $J_M(t)$  is the membrane current at time t. When V(t) reaches some predetermined threshold value, a  $\delta$ -function representing the emission of a spike is added to the temporal response of the neuron. After the spike occurs, the membrane voltage is reset followed by a short refractory period, typically on the order of a few milliseconds, where no additional spiking can occur.

LIF neurons can approximate the spiking behavior of neurons only to the level of the temporal occurrence of action potentials. The spikes themselves have no shape as they are represented by a  $\delta$ -function, and the neurons are stereotyped so that no adaptation to certain input patterns is possible. Extensions to the LIF model exist, such as the Adaptive Exponential LIF model [12], that attempt to retain the simplicity of the original while adding additional representative features.

#### **Hodgkin-Huxley**

While the LIF model neuron can represent simple spiking behavior, the spikes do not arise naturally from the model and instead are simply added when needed. The *Hodgkin-Huxley (HH)* model [33], on the other hand, does give rise to the observed rapid depolarization and subsequent hyperpolarization seen with real action potentials. It accomplishes this by modeling at the level of ion channel kinetics. While this model has had great success in characterizing the behavior of a single neuron, it is computationally expensive due to the number of simultaneous differential equations that must be evaluated. It also has a large number of system parameters that need to be specified for the type and environment of the neuron being modeled which must be determined experimentally. As such, it is generally not used when attempting to model large-scale networks.

#### Phenomenological

Phenomenological neural models try to combine the success of the HH model for representing a large variety of spiking dynamics with the computational efficiency of the LIF model. Several models have been developed, such as the  $\theta$ -neuron [22] and the Izhikevich model [34]. The latter has seen use in very large-scale simulations [3] as it is able to represent a wide variety of neural spiking behaviors while maintaining a quadratic term as the most computationally expensive element whereas the  $\theta$ -neuron model requires trigonometric functions while those closer to the HH model still rely on exponentials.

While phenomenological models are able to represent complex spiking behavior cheaply, they do this at the cost of not having any physiological basis for the parameters and terms in the model equations, the former generally obtained analytically through sweeps of the parameter space.

#### 2.2.5 Neural Communication

When modeling connected networks of neurons, synaptic communication must be modeled in addition to neural spiking dynamics. This too can be done at varying degrees of detail, with synaptic strength representations ranging from simple weights represented as scalar values to multiple ion channel models, each with their own dynamics. The particular synaptic model used in the simulations presented later is based on PSCs.

As mentioned in Section 2.2.1, PSCs are generated by neurotransmitters in the synaptic cleft binding to receptors in the membrane of the neuron. The neurotransmitters do not immediately bind and then disappear after an action potential event, rather they linger in the synapse until they are taken back up into the axon terminal of the efferent neuron or diffuse elsewhere. This allows the PSC to rise or decay relative the occurrence of spikes over time, creating a concept of spike history at the dendrite. Computationally, this is achieved by convolving the spikes with a linear filter given by

$$h_{PSC}(t) = t^n e^{-t/\tau_{syn}}, (2.2)$$

where t is time, n is the order of the filter, and  $\tau_{syn}$  is the synaptic time constant. From a signal processing standpoint this is an example of a causal filter. Non-causal filters, which may be more optimal, do not exist in real-time systems, thus making the choice of a causal filter more appropriate for modeling neural communication in simulation.

#### 2.2.6 Analysis Framework

Not only are there several ways of constructing a model environment for simulating neural activity, there are also a myriad ways to record and analyze that activity. The choice of analysis framework is, like the physiological model under evaluation, dependent on the research question and the way the neurons are expected to represent information.

#### **Information Representation**

**Firing Rate** Some types of neurons encode information in the frequency of action potentials emitted over a given time window. In these cases, the *firing rate* (spikes per second) of the neuron is more interesting than the individual spike events, so only the rate is determined and stored. A classic example of where this occurs in nature was demonstrated by Georgopoulos et al. [25] in showing that certain neurons fired more rapidly than others given a particular directed arm reach event.

The rate-based framework for neural activity is well established, but does have its weaknesses. Any information encoded in the spacing between spikes or the shape of the action potentials is lost. The communication between neurons is also reduced in sophistication, allowing for only a small range of strategies, such as simple weighting.

**Temporal Spiking** Instead of averaging spikes over time, the individual spiking events themselves can be recorded and analyzed. This approach gives a much smaller level of granularity and is easier to manage computationally as no additional averaging step is required. However, if the information encoded by the neurons is indeed rate-based, it will be more difficult to identify. Spike-based frameworks are suited to simulations where the shape pr timing of the neural response is important as well as when detailed synaptic communication is required.

#### **Information Decoding**

**Linear Filtering** One method for decoding the information represented by a neural population is to use linear filtering, a common signal processing technique. The linear filter approach scales and combines the time-varying signals of the neural responses using a linear transform defined by a vector of decoding weights. To reconstruct the signal of interest, the decoding weights are simply multiplied against the response signal. Finding the optimal decoding weights can be very difficult, however.

**Bayesian Approaches** Another popular technique is to use Bayesian analysis to conduct probabilistic approaches to evaluating the neural code. Generally, these methods attempt to determine the information represented by the neurons by evaluating the probability of observing a certain firing rates under certain conditions. Bayesian analysis has proven successful [20], but suffers from computational complexity making in unsuitable for real-time applications.

#### 2.3 Neural Network Simulation

As indicated previously, the type and range of models employed by a researcher is dependent on the question under study. Most of the broad areas of interest have corresponding software tools that exist to enable ease of creation and simulation of models. For instance, NEURON [32] and GENESIS [11] are simulation packages geared toward studying models of complicated neuron morphology while NEST [18] and Brian [27] are more focused on large scale point-neuron network dynamics. All of these tools are CPU-based, and, at present, do not incorporate any form of GPU-based acceleration.

These are only a small sample of the many simulation tools that exist (see [13] for a review), and, while they enable researchers to focus more on modeling and less on technical implementation, there still exists a certain amount of challenge in configuring the tools and expressing the desired model in a way that the tool requires. In an attempt to standardize and simplify model definitions, tools are actively being developed such as PyNN [17], a Python-based framework for interfacing with several popular simulation packages, and NeuroML [26], an XML-based model and network specification language.

#### 2.3.1 Simulation Process

The general process followed by most simulation tools is to evaluate the neural models' required differential equations, usually through the use of an iterative solver such Runge-Kutta. These evaluations happen in either a time- or event-driven fashion [13]. In the time-driven scenario, the neurons (or compartments of the neurons) are evaluated in synchronous lock-step with a single simulation-wide clock. It is possible for somewhat asynchronous evaluation, especially in parallel environments, though the overall simulation process would still need a way to track where in simulation time all the elements were.

For event-driven environments, each neuron's state is only evaluated when an event such as a spike is sent to it. This allows for a much more asynchronous execution of the simulation. Agent-based models [10] are an example of a purely event-driven simulation, where each neuron is acting as an independent process tending to its own internal state and communication is handled in asynchronously. This is the most akin to neurons in the brain, but also the most complicated and resource intensive to simulate for any significantly-sized neural population.

#### 2.3.2 Simulating Neural Networks on the GPU

The GPU provides an intriguing platform for neural network simulation because its massive parallelization and shared memory model allow it to overcome many of the computational bottlenecks of the event-driven model while still maintaining large population sizes. It is no surprise, then, that previous work has been done in this area.

One of the earliest attempts was by Bernhard and Keriven [8], who used the GPGPU approach to demonstrate a simple spiking neural network application on a GPU. Recently, Nageswaran et al. developed a spiking neural network simulator on an NVIDIA GPU that can handle up to 10 million synaptic connections between 100 thousand neurons at near real-time [43]. This simulation tool was developed with an eye toward maximizing computational efficiency in order to maximize the size of the neural populations simulated. It accomplishes this by using Izhikevich model [34] neurons and overlapping neural and synaptic updates within thread blocks. The approach taken in Chapter 4 varies primarily from this model in that it uses a more physiologically-driven agent-inspired model for handling neural updates. While this doesn't

achieve the same level of performance for the simple populations described in [43], it was designed for a greater range of flexibility in customizing the simulation environment.

#### CHAPTER 3

### Self-Organizing Maps

One of the classic neural network models, the Self-Organizing Map (SOM), is used for multi-dimensional data analysis and visualization. Also referred to as a Kohonen network, the SOM was originally described by Teuvo Kohonen in 1982 [39] and is built on two key concepts: a competitive, or *winner-take-all* neuron response to an input and a topological arrangement of neurons. The SOM has found success in clustering, dimensionality reduction, and other data mining applications.

The work presented in this chapter describes an implementation of the SOM training algorithm on a GPU using CUDA. This was conducted as a proof of concept exercise to evaluate how neural networks could be implemented and potentially visualized using the GPU as an accelerator. First the SOM training algorithm is described, followed by the strategy used in implementing the algorithm on the GPU. Finally, performance results comparing the GPU version to a similar, CPU-only implementation are provided and analyzed with additional discussion regarding visualization efforts.

## 3.1 SOM Algorithm

In order to apply the SOM to a data set, the configuration of the neural network must defined. This involves decisions regarding the number of neurons in the network as well as their topographical layout. Once established, the network is trained on the data set by presenting one data point at a time as input. Once training is complete, the results can be analyzed by searching

for common elements in the data points associated with a particular neuron. These steps are described in more detail in the following sections.

#### 3.1.1 Network Configuration

The first step required is to determine the topological arrangement of neurons. Frequently this is in a 2-dimensional grid, though 3-dimensional arrangements such as cubes, tori, or other custom shapes are also possible. The selection of topology is based on assumptions about the potential relationships within the data as well as convenience in representing and visualizing the resulting network. The number of neurons in the grid should also be chosen to allow enough distinct groupings to appear, as too few causes most data points to lump together, while too many divides each data point into its own group, with both cases failing to produce meaningful or interesting associations.

Each neuron is assigned a *weight*, or value, that represents its relationship to the data set under study. This weight takes the form of a multi-dimensional vector that has as many elements as the data. For instance, if training on genomic sequence data, the neurons would have weight vectors long enough to account for each base pair. These weights are initialized to random values so as not to bias the training process.

#### 3.1.2 Training

To train the network, the SOM uses a machine learning algorithm. There are two primary approaches to machine learning: supervised and unsupervised. In supervised learning, the expected output is provided along with the input to evaluate the success of the network. Learning is accomplished by adjusting weights to minimize the error between the actual and expected output. In unsupervised learning, no expected output is provided. Instead of adjusting weights based on the error, the weights are updated to closer match the input. The SOM uses an unsupervised learning approach.

In addition to being unsupervised, the learning process is also *competitive*. Competitive learning means that only certain neurons in the network actually modify their weights in response to an input. In this particular case, the neuron that most closely matches the input is designated the

winner, or *Best Matching Unit (BMU)* (Figure 3.1). This neuron, and, to some extent, its neighbors, are the only neurons to train their weights against the input.

Figure 3.1: A 25 neuron SOM configured in a 5x5 grid. The orange neuron represents the BMU, while the shaded area around it is the neighborhood of effect.

The formal training algorithm is presented in Algorithm 1. In this process, p is one data sample from the data set and  $\alpha$  is the *learning rate*. The learning rate is typically expressed as a percentage and controls how strongly the neuron weight is adjusted toward the input value. A high learning rate may result in instability in that neurons will be overly sensitive to each individual input. A low learning rate, on the other hand, may never satisfactorily train the network. A typical value for the learning rate is 5%. The weight of neuron n is represented by w(n), while d(w(n), p) is the distance measure of the input to the neuron's weights. This comparison can be any kind of distance or similarity measurement, though a common choice is Euclidean distance. Finally, N(n,bmu) is the *neighborhood scaling function*, an additional scaling factor applied to the

learning rate of each neuron dependent on how close it is to the BMU in the network topology. Examples of neighborhood functions are rectangular windows (all neurons within a certain distance get full learning rate while the rest have no change), triangular or Guassian curves (the farther away from the BMU, the less influence the input exerts), and the Mexican Hat curve (like the Guassian, only the curve can go negative, so neurons a certain distance away from the BMU have a negative learning rate).

Each data element is presented to the SOM for training one at a time. Often several iterations of training are conducted, with the learning rate or neighborhood size decreasing after each full iteration until the SOM has reached equilibrium or a predefined maximal number of iterations have passed.

#### Algorithm 1 SOM Algorithm

```

1: procedure SOM(p, \alpha)

for all n do

2:

d_n = d(w(n), p)

3:

if d_p < d_{min} then

4:

d_{min} \leftarrow d_p

5:

bmu \leftarrow n

6:

end if

7:

end for

8:

9:

for all n do

w(n) \leftarrow w(n) + N(n, bmu) * \alpha * (p - w(n))

10:

end for

11:

12: end procedure

```

#### 3.1.3 Analysis

Once the SOM has been sufficiently trained, the researcher can analyze and review the results. This is frequently accomplished through some form of visualization, where it is possible to discern which data elements are aligned with each neuron. In some situations, simple color coding is capable of conveying a clear picture of how certain classes of data elements align, while interactive interfaces or additional processing is needed to extract the groupings from the SOM in order to determine if any new knowledge can be gained.

```

__global___ void

findDistance(float *dist, float3 *som, float3 p)

{

int idx = blockIdx.x * blockDim.x + threadIdx.x;

float x = som[idx].x - p.x;

float y = som[idx].y - p.y;

float z = som[idx].z - p.z;

dist[idx] = x*x + y*y + z*z;

}

```

Listing 3.1: findDistance kernel definition

# 3.2 GPU Approach

The SOM contains several properties that make it an attractive neural network to implement on a GPU. First, operations required by the training algorithm are data parallel, making it an ideal fit for the massive parallelism of the GPU. Second, the visualization aspect of SOM analysis aligns directly with the GPU's primary purpose. Whereas existing SOM implementations [49] use 2D visualizations, 3D views could be created with the ability to rotate and zoom within the structure for a more interactive experience.

The first step in parallelizing the SOM algorithm with CUDA was to identify where the dependent steps were. As each training step must happen sequentially, the only places where parallelism was possible was a nearest neighbor search used to identify the BMU and the updating of the neuron weights.

## 3.2.1 BMU Identification

Searching for the nearest neighbor to a point in a given space has been studied extensively [4, 52, 6]. For this implementation, neurons were arranged in a 2D square grid configuration and Euclidean distance was used to determine closeness of the neurons to the input. The neurons were treated as a single 1D array of N-element vectors, with each thread calculated the distance between the input and a neuron then stored that value in an intermediate buffer (Listing 3.1). A parallel minimization reduction operation was performed on the distance buffer to identify the ID of the neuron with the closest distance and a combination of division and modulus operations were used to determine the respective x and y coordinates of the BMU in the grid (Listing 3.2).

```

min = cublasIsamin(n, d_dist, 1);

bmu = make_uint2(min % w, min / w);

```

Listing 3.2: Determining BMU from distance calculations

```

__global___ void

updateWeights(float3 *som, uint2 bmu, float3 p, float radius, float alpha, int

width)

{

int x = blockIdx.x * blockDim.x + threadIdx.x;

int y = blockIdx.y * blockDim.y + threadIdx.y;

int idx = y * width + x;

int u = x - bmu.x;

int v = y - bmu.y;

int d = u*u + v*v;

if(d < radius) {

som[idx].x += alpha*(p.x - som[idx].x);

som[idx].y += alpha*(p.y - som[idx].y);

som[idx].z += alpha*(p.z - som[idx].z);

}

}</pre>

```

Listing 3.3: updateWeights kernel definition

# 3.2.2 Update Neighborhood

Once the BMU has been identified, the bounding box surrounding the affected neural neighborhood was identified and used to quickly reduce the number of neurons that needed to be evaluated. Each thread determined the Euclidean distance of a neuron to the BMU and adjusted the values accordingly using a step function and a fixed learning rate (Listing 3.3).

### 3.3 Results

A 24-bit bitmap image (Figure 3.2) was chosen as a data source, with each pixel representing a single 3-dimensional vector input. Pixels were presented to the SOM one at a time, starting at the bottom-left of the image and progressing in a left-to-right, bottom-to-top fashion. The learning rate was fixed at 0.05 and a rectangular windows of width 5 was used to determine neighborhood scaling.

The GPU performed worse than an equivalent serial CPU implementation for small grids then eventually achieved up to a 2.5x speedup for very large grids (Figure 3.3). This is not

Figure 3.2: 2400 x 1800 pixel bitmap image [47] used as the input data source. Licensed under CC-BY-NC-2.0.

unexpected, as the GPU incurs additional time overhead in both data transfer to and from the device as well as kernel function invocation. For such a relatively straightforward algorithm, the data set needs to be significantly large for the GPU's parallelism to achieve noticeable gain.

# 3.4 Discussion

As each input data point has to be presented one at a time, the potential for performance gains is confined to the two steps of the training algorithm. For very large data sets, such as several million pixel images, tiny performance gains in a single iteration translate to significant benefit over the course of a complete run. As there were relatively only small number of neurons that needed to be evaluated during the update phase, the GPU offered little in the way of benefit over the CPU. Where the GPU managed to outperform the CPU was in identifying the BMU, though that gain was small only when compared to a naive CPU implementation of a nearest neighbor search i.e. iterating through all points and keeping track of the one with the shortest computed distance.

Figure 3.3: Performance of the GPU version versus the CPU version of SOM training for a single iteration. Speedup is defined as GPU/CPU.

There are much more efficient ways to do multi-dimensional searches, such as using kd-trees [7]. The main drawback of the kd-tree data structure is that it is expensive to generate. This is fine for multiple searches against a static data set, but the SOM neurons update every time step and in what would be many disparate locations in the tree until well into the training. Some work had been done relating to ray-tracing on the GPU where kd-trees were generated for each frame of an animation [53], but the times reported, while encouraging for real-time video rendering, were too slow to be useful for SOMs. Splay trees [48] and R-trees [29] also seemed promising, but neither presented an obvious parallel implementation that effectively maintained performance across multiple updates to the tree at each iteration.

#### 3.4.1 Visualization

Because of their topographical nature, SOMs can be visualized in a number of ways. One such approach is to translate the weights of the trained SOM into RGB values and present the SOM as a bitmap. This allows a quick view into how the SOM was clustered and may provide some insight into either the input data or the SOM itself. Bitmap representations of the SOM state at various points during the training (Figure 3.4) as well as at completion (Figure 3.5) were captured. Given that the source data are also pixels, the SOM is simply clustering the palette of the

original image into blobs whose general shape and location are dependent on the psuedorandom number generator seed used to initialize the network. While this particular example does not provide much useful information, it does present an interesting application for computer-generated art that may be worth future exploration.

Additionally, one of the attractive features of GPUs for neural networks is that the integration with standard computer graphics APIs such as OpenGL [51] allows network activity to be visualized in real-time. The SOM implementation was incorporated into a simple OpenGL application (Appendix B) that represented the SOM as an image on screen (Figure 3.6). Updates to the neuron values could be observed as slight changes to the image as the pixel RBG values were updated. While of limited value for the actual purpose of the SOM, it does demonstrate the ability to visualize the evolution of a neural network which may provide additional insight when applied to more realistic neural models.

Figure 3.4: State of the SOM as rendered by a bitmap image at various stages in training. One line = 1800 inputs.

# 3.5 Conclusion

Implementing and visualizing the SOM neural network on the GPU was a beneficial and enlightening exercise. Valuable experience was gained by programming in the CUDA environment, and many of the realities faced in attempting to parallelize applications were

1800 lines

Figure 3.5: Final state of the SOM after all pixels had been presented.

Figure 3.6: A screen capture of an OpenGL application depicting the training of a SOM in real time. The source input used was related to Marquette University, thus the emergence of gold and blue.

encountered. For instance, the limitations in performance gains through parallelization imposed by Amdahl's Law was quite apparent, give the highly serial nature of the training process.

Furthermore, overall performance improvement only appeared when the problem size was

increased enough for the speedup gains in parallelization to overcome the overhead costs incurred by the GPU platform.

It is unclear what practical applications exist for SOMs large enough to benefit from GPU acceleration. The data elements used in testing were relatively small in both dimensionality and value, so it is possible that applications with more complicated data such as text mining or bioinformatics would see greater benefit. Exploring these possible applications as well as enhancing the visualization tool are both solid avenues for further study.

## **CHAPTER 4**

# **Spiking Neural Networks**

The SOM from Chapter 3 is a classical neural network that was successfully implemented on a GPU. The SOM does not, however, accurately represent actual biological neural networks as it lacks inter-neuron communication, time-dependent behavior, and several other features. The work presented in this chapter demonstrates the design and implementation of a recurrent biological neural network simulator on a GPU using CUDA. For a connected network, neuron communication becomes an important and limiting factor of the simulation. In a fully connected network — one where each neuron has a directed connection, or synapse, to every other neuron including itself — the number of synapses is equal to the square of the number of neurons. Even at small percentages of full connectivity, the number of synapses is orders of magnitude larger than the number of neurons. Communication quickly dominates the computational time of a simulation. As the neurons and synapses have no direct effect on each other at each time step of the simulation, it is possible to evaluate them in parallel, making the GPU an ideal platform to develop a simulator.

The simulation environment developed models network communication through synaptic transmission of action potentials, while leaky integrate-and-fire neurons were used to handle the spiking dynamics. The key motivating design principle, however, was to map the massively parallel nature of the GPU to the naturally concurrent processing exhibited by neurons. An agent-inspired approach was chosen that maps one neuron per thread. The neuron itself was broken down into its functional components of dendrites, soma, axon, and synapses. Each maintained the one component per thread design with the exception of the synapse which was handled by a thread block. The rest of this chapter details the design decisions and implementation

strategies adopted, concluding with performance results and analysis compared to an MPI-based version of the same general simulation.

# 4.1 GPU Approach

The recurrent neural population simulation is comprised of three main parts: initialization, execution, and output. In the initialization phase, the population's individual neuron characteristics and network topology are read in from specification files. As defining the exact configuration for each neuron and synapse quickly becomes infeasible as the population size grows, these files are generated by a higher level interface that randomly generates parameters based on specified ranges.

Once the data structures needed by the simulation have been fully initialized and the data to be monitored for later output defined, the execution of the simulation begins. In this phase, the state of each neuron is updated once per time step according to its dynamics based on input from external stimuli and communication from other neurons. The execution lasts until the total prescribed simulation time has been reached, at which point results of any data monitoring are output to a file for off-line processing and review. In this implementation, all initialization and output were handled by the CPU while the GPU was employed to enable massive parallelism in the execution step.

#### 4.1.1 Data Model

The data model chosen to represent the system state of the neural network under simulation was based on neuron morphology. An agent-inspired system [10] was conceived that employed a one-to-one mapping between processing elements and neurological structures. In order to accomplish this, several data structures were defined to represent the various active and passive components of the neurons in the population (Table 4.1).

The Neuron, LIFNeuron, and Synapse structures represent passive information about the simulated neurons, such as number of dendrites, neural dynamic properties, and connectivity.

These are constant values — once initialized they do not change throughout the course of a simulation. The active, or dynamic, properties of the neurons are represented by the Dendrite,

| Structure | Neural Analog    | <b>Data Elements</b>             | Description                                     |

|-----------|------------------|----------------------------------|-------------------------------------------------|

| Neuron    | The Cell         | dendriteOffset<br>dendriteLength | Address information of dendrites                |

|           |                  | pscOffset<br>pscLength           | Address information of PSC filter               |

| LIFNeuron | Spiking Dynamics | tauRef                           | Action potential refractory period time         |

|           |                  |                                  | constant                                        |

|           |                  | tauRC                            | Neural membrane RC time constant                |

|           |                  | Rleak                            | Neural membrane resistance                      |

|           |                  | Vth                              | Membrane potential at which an action           |

|           |                  |                                  | potential is generated                          |