#### **Marquette University**

## e-Publications@Marquette

**Electrical and Computer Engineering Faculty** Research and Publications

Electrical and Computer Engineering, Department of

10-5-2017

## An Advanced Three-Level Active Neutral-Point-Clamped Converter With Improved Fault-Tolerant Capabilities

Ramin Katebi Marquette University

Jiangbiao He Marquette University

Nathan Weise Marquette University, nathan.weise@marquette.edu

Follow this and additional works at: https://epublications.marguette.edu/electric\_fac

Part of the Computer Engineering Commons, and the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Katebi, Ramin; He, Jiangbiao; and Weise, Nathan, "An Advanced Three-Level Active Neutral-Point-Clamped Converter With Improved Fault-Tolerant Capabilities" (2017). Electrical and Computer Engineering Faculty Research and Publications. 300.

https://epublications.marquette.edu/electric\_fac/300

#### **Marquette University**

## e-Publications@Marquette

# Electrical Engineering Faculty Research and Publications/Opus College of Engineering

This paper is NOT THE PUBLISHED VERSION; but the author's final, peer-reviewed manuscript. The published version may be accessed by following the link in the citation below.

*IEEE Transactions on Power Electronics*, Vol. 33, No. 8 (2018): 6897-6909. <u>DOI</u>. This article is © Institute of Electrical and Electronics Engineers and permission has been granted for this version to appear in <u>e-Publications@Marquette</u>. Institute of Electrical and Electronics Engineers does not grant permission for this article to be further copied/distributed or hosted elsewhere without the express permission from Institute of Electrical and Electronics Engineers.

## An Advanced Three-Level Active Neutral-Point-Clamped Converter With Improved Fault-Tolerant Capabilities

#### Ramin Katebi

Department of Electrical and Computer Engineering, Marquette University, Milwaukee, WI Jiangbiao He GE Global Research, Niskayuna, NY

Nathan Weise

Department of Electrical and Computer Engineering, Marquette University, Milwaukee, WI

#### Abstract:

A resilient fault-tolerant silicon carbide (SiC) three-level power converter topology is introduced based on the traditional active neutral-point-clamped converter. This novel converter topology incorporates a redundant leg to provide fault tolerance during switch open-circuit faults and short-circuit faults.

Additionally, the topology is capable of maintaining full output voltage and maximum modulation index in the presence of switch open and short-circuit faults. Moreover, the redundant leg can be employed to share load current with other phase legs to balance thermal stress among semiconductor switches during normal operation. A 25-kW prototype of the novel topology was designed and constructed utilizing 1.2-kV SiC metal-oxide-semiconductor field-effect transistors. Experimental results confirm the anticipated theoretical capabilities of this new three-level converter topology.

#### Keywords

Active neutral-point-clamped (ANPC) converter, current sharing, fault-tolerant operation, open circuit, redundant leg, short circuit

#### SECTION I.

#### Introduction

Low harmonic distortion in the output, high dc-bus voltage, decreased common-mode voltage and reduced dv /dt stress have been motivating the adoption of multilevel power converters in numerous industrial applications [1]. However, compared to the hardware topologies of two-level converters, multilevel converters typically use a large number of semiconductor switching devices in the circuit topologies. Accordingly, such increased hardware complexity degrades the reliability of multilevel converters. Particularly, for multilevel converters used in safety-critical applications, such as more-electric aircrafts (MEA), uninterruptible power supplies (UPS), high-power medical instruments, and electric/hybrid vehicles (EV/HEV), fault-tolerant operation capability under the condition of device open-circuit and short-circuit switching faults will be of significant importance.

The three-level neutral-point-clamped (3L-NPC) converter is one of the most popular topologies used in industry today among the various circuit topologies available for multilevel converters [2]–[5]. However, unequal power loss distribution among the semiconductor devices is a disadvantage of the 3L-NPC converter and may cause device failures under thermal overload conditions [6]. This is mainly because that the inner switches in the 3L-NPC converter are turned ON longer than the other switches, which results in more conduction loss. Furthermore, the clamping diodes in the topology force the converter to have just one neutral path per output current direction. Subsequently, the converter output current must be constrained to avoid excessive junction temperature in the inner devices [6].

To enhance the reliability of the three-level converters, a few fault-tolerant converter topologies have been proposed [7]– [18]. First, the inherent fault-tolerant capability of the conventional NPC converter was investigated in [7]. In this paper, the fault-tolerant strategies of a three-phase three-level NPC converter under singular short-circuit faulty condition of insulated-gate bipolar transistors (IGBTs) and clamping diodes were discussed. However, it shows that a few large voltage space vectors are lost for each of the fault cases, which indicates the necessity of derated operation of the NPC converter during the postfault stage. Specifically, the NPC converter cannot operate at a modulation index higher than 1/  $3\sqrt[4]{7}$ ]. Similarly, another fault-tolerant solution for the outer switch open-circuit faults in the NPC rectifier of a three-level wind turbine back-to-back power converter was developed in [8]. The fault-tolerant operation for the outer switch faults in the NPC rectifier was achieved based on modifying the modulation reference voltage to connect the associated faulty leg to the dc-bus neutral point. A hybrid fault-tolerant three-level NPC converter was introduced in [9]. The fault-tolerant capability of such topology is based on the introduction of a fourth flying capacitor phase leg to provide an active neutral point for the original three NPC phase legs. The four-leg NPC topology is able to disconnect the failed

phase leg and connect the load to the fourth leg for any type of IGBT failures (open-circuit or shortcircuit mode). However, it requires significantly redundant passive and active power devices, which makes the hardware circuit much more complicated. In [10], the authors investigated the inherent fault-tolerant capability of three-level active neutral-point-clamped (3L-ANPC) converters. However, at some of the fault scenarios, the 3L-ANPC converter has to be controlled with decreased modulation indices. Therefore, this would not be suitable for applications demanding rated output voltages such as EV/HEV, UPS, and the like. A four-leg fault-tolerant solution for NPC converters was introduced in [11]. The purpose of adding this fourth phase leg is to provide a back-up to the NPC converter in case of any switch faults occurring in one of the three main legs, while this fourth leg can also be used to provide a stiff neutral-point voltage under healthy conditions. Consequently, the low-frequency voltage oscillation that usually appears at the dc-bus neutral point is eliminated, and the PWM voltage space vectors can be more intensively utilized to optimize the converter efficiency and harmonic distortions, instead of being considered for controlling the dc-bus neutral-point voltage. However, all these benefits are achieved at the cost of adding more redundant devices to the converter topology, which specifically include at least one capacitor, four fast-acting fuses, six IGBT modules, and three TRIACs. Another fault-tolerant solution for NPC converters was introduced in [12]. In this solution, three pairs of thyristors and fuses have been added to the NPC converter circuit topology to improve its faulttolerant capability. The purpose of adding these thyristors is to avoid the short circuit of dc-bus capacitors when one of the switches has a short-circuit fault. One advantage of this fault-tolerant solution is that no derating is required during fault-tolerant operation. However, there are two potential concerns with this solution. The first concern is that the fuses used in the fault-tolerant circuit topology typically have much larger clearing 12t characteristic than the bond wires in general IGBTs, which indicates that the related IGBTs may fail prior to the blow out of the fuses. The second concern is that some of the IGBTs will encounter large voltage stress if there is a short-circuit fault in the seriesconnected adjacent switch on the same converter leg. Recently, another fault-tolerant topology for three-level T-Type NPC converter was developed and presented in [13], [17], and [18]. This four-leg fault-tolerant T-Type converter can tolerate any open-circuit faults and part of the short-circuit faults while maintaining rated voltage output at any fault scenarios. In this paper, an advanced 3L-ANPC (A3L-ANPC) converter will be introduced that can overcome the drawbacks of the conventional faulttolerant solutions for NPC converters.

The identifications of the faulty switches in this paper rely on existing fault diagnostic techniques. Specifically, the online diagnosis of open-circuit switching faults is achieved by monitoring the variations of the dc-bus neutral-point current under given switching states. Each open-circuit fault scenario in the ANPC converter can be identified by comparing the detected value with the expected value under healthy condition. The expected value of the dc-bus neutral-point current is a function of the converter switching states and the instantaneous three-phase currents. The real-time information of the converter switching states and three-phase currents is typically available in the controller. The detailed implementation of such fault diagnosis method has been developed and introduced in [16], [19], and [20], and therefore, will not be repeated here. Unlike the diagnosis of open-circuit switching faults, the detection of the short-circuit faults requires faster response (typically, around a few microseconds). This is because that the general short-circuit withstanding capability of industrial Si IGBT or SiC MOSFET is no more than 10  $\mu$ s. Therefore, diagnosis of short-circuit switching faults is generally implemented in gate driver circuits. In this paper, the short-circuit fault diagnosis is achieved by using the desaturation detection circuit integrated in the gate drivers. The working principle of desaturation detection circuit has been presented in the literature [21].

The remaining content of this paper will be organized as follows. First, the operational characteristics and the fault-tolerant capability of the conventional 3L-ANPC converters will be reviewed and discussed in Section II. Second, based on the drawbacks of the fault-tolerant capability of the 3L-ANPC converter, an A3L-ANPC converter will be proposed and introduced in Section III. Experimental verification of the A3L-ANPC converter under various device fault scenarios will be given in Section IV. Another promising advantage with this proposed A3L-ANPC converter, namely, the current sharing characteristic by leveraging the redundant leg, will be presented and experimentally verified in Section V. Moreover, improved fault-tolerant capability of the proposed A3L-ANPC converter will be compared with the conventional 3L-ANPC converter in Section VI. Finally, conclusions are drawn in Section VII.

#### SECTION II.

#### Conventional 3L-ANPC Converter

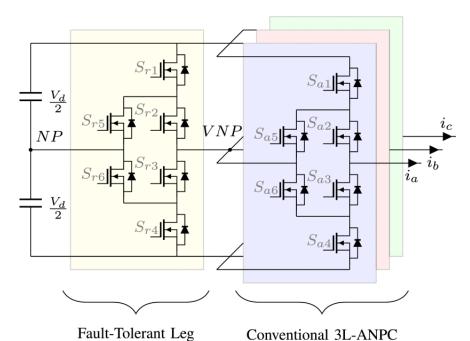

In contrast to the 3L-NPC converter, the 3L-ANPC converter has an additional active switch in antiparallel connected with each clamping diode along the neutral paths [6]. The circuit topology of the 3L-ANPC converter is shown in Fig. 1. The additional active switches in a 3L-ANPC converter provide more zero switching states to evenly distribute the losses and device junction temperatures. The 3L-ANPC converter can commutate current to the upper neutral path or the lower neutral path for both positive and negative phase current. All the switching states of the 3L-ANPC converter are given in Table I. As it can be seen, the upper neutral path (0U1 and 0U2) can be used when switches  $S_{a2}$  and  $S_{a5}$  are ON, while  $S_{a1}$ ,  $S_{a3}$ , and  $S_{a6}$  are OFF with  $S_{a4}$  being ON for state 0U1 or OFF for state 0U2. The lower path (0L1 and 0L2) can be used when  $S_{a3}$  and  $S_{a6}$  are ON, while  $S_{a2}$ ,  $S_{a4}$ , and  $S_{a5}$  are OFF with  $S_{a1}$  being ON for state 0L1 or OFF for state 0L2. Accordingly, the 3L-ANPC converter can more evenly distribute device losses by selecting a zero state among four zero switching states available for commutating the neutral-point current. For example, the 0L1 state can be chosen to prevent switching loss in  $S_{a1}$  when switching the phase output between the positive dc-bus and the neutral point.

**Fig. 1.** Circuit topology of the proposed A3L-ANPC converter.

**TABLE I** Switching States of the A3L-ANPC Converter Phase-A Leg Under Normal Operation

|        | Switch on Phase-A Leg |          |          |          | Voltage Balancing |          |     |

|--------|-----------------------|----------|----------|----------|-------------------|----------|-----|

| Output | $S_{a1}$              | $S_{a2}$ | $S_{a3}$ | $S_{a4}$ | $S_{a5}$          | $S_{a6}$ |     |

| P1     | 1                     | 1        | 0        | 0        | 0                 | 0        | No  |

| P2     | 1                     | 1        | 0        | 0        | 0                 | 1        | Yes |

| 0U2    | 0                     | 1        | 0        | 0        | 1                 | 0        | No  |

| 0U1    | 0                     | 1        | 0        | 1        | 1                 | 0        | Yes |

| 0L1    | 1                     | 0        | 1        | 0        | 0                 | 1        | Yes |

| 0L2    | 0                     | 0        | 1        | 0        | 0                 | 1        | No  |

| N1     | 0                     | 0        | 1        | 1        | 0                 | 0        | No  |

| N2     | 0                     | 0        | 1        | 1        | 1                 | 0        | Yes |

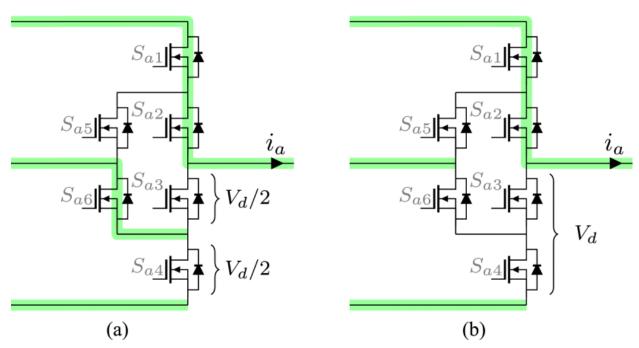

The additional active switches in a 3L-ANPC converter can also provide voltage balancing between the switches  $S_{a1}$  and  $S_{a2}$ , as well as that between the switches  $S_{a3}$  and  $S_{a4}$ . As is shown in Fig. 2(a), when the Phase-A output is connected to the positive dc bus, the device  $S_{a6}$  is turned ON to ensure equal voltage sharing between  $S_{a3}$  and  $S_{a4}$ . Similarly, when the Phase-A output is connected to the negative dc bus, equal voltage sharing between  $S_{a1}$  and  $S_{a2}$  is ensured by turning ON  $S_{a5}$ . As a result, voltage balancing resistors across the switches can be omitted.

**Fig. 2.** Voltage balancing between  $S_{a3}$  and  $S_{a4}$  in a 3L-ANPC converter. (a) With voltage balance. (b) Without voltage balance.

Fig. 2(b) depicts a normal switching state that does not ensure voltage balance across the two lower switches. The absence of a voltage balancing resistor network along side slight physical device variations results in an undetermined voltage split between switches  $S_{a3}$  and  $S_{a4}$ .

The 3L-ANPC converter can operate when a single or multiple device failures occur in one or more phases, because the switches  $S_{a5}$  and  $S_{a6}$  provide additional fault-tolerant capabilities compared to the 3L-NPC converter [10]. However, the 3L-ANPC converter has to be operated with reduced output voltage for some of the device faults.

For a device open-circuit failure, 0U1 or 0U2 must be used for commutating the neutral current if  $S_{a6}$  has an open-circuit fault and 0L1 or 0L2 must be used for commutating the neutral current if  $S_{a5}$  has an open-circuit fault. If  $S_{a1}$  through  $S_{a4}$  have an open-circuit fault, the output of the faulty phase must be connected to the neutral point and the maximum modulation index has to be reduced from  $2/\sqrt{3}$  to  $1/\sqrt{3}$  [10].

The switching states are selected to avoid a shoot through between the positive dc bus, negative dc bus, and the neutral point during a device short-circuit failure event. The faulty phase can continue to generate three-level output if a short-circuit fault takes place in  $S_{a1}$  or  $S_{a4}$  provided these devices can tolerate the full dc bus voltage. If the remaining devices have a short-circuit fault, the faulty phase leg is required to be connected to the neutral point and the maximum modulation index is diminished to  $1/\sqrt{3}$  [10]. Alternatively, if the faulty phase is always connected to the neutral point, the switches are not subjected to the full dc bus voltage but the maximum modulation index becomes  $1/\sqrt{3}$  resulting in reduced output power [10].

The reliability analysis in [10] reports that the 3L-ANPC converter is more reliable than the 3L-NPC converter when a reduced output power is permissible. The 3L-ANPC is 10% more reliable for a single device short-circuit failure and 8.5% more reliable for single device open-circuit failure compared to 3L-NPC [10]. If a reduced output voltage and or power is not allowed, the two converters will have a similar reliability for open-circuit failures, while the 3L-NPC converter will have a higher reliability for short-circuit failures [10].

Reduced output voltage and power is not allowed in certain mission critical systems such as MEA, UPS, and EV/HEV. As a solution, an A3L-ANPC converter topology was introduced in [22] that can maintain full output power and voltage during both short-circuit and open-circuit fault events. The full investigation of the capabilities of the A3L-ANPC converter and a thorough comparison with the 3L-ANPC converter will be provided.

#### SECTION III.

## Fault-Tolerant Operation of the Proposed A3L-ANPC Converter

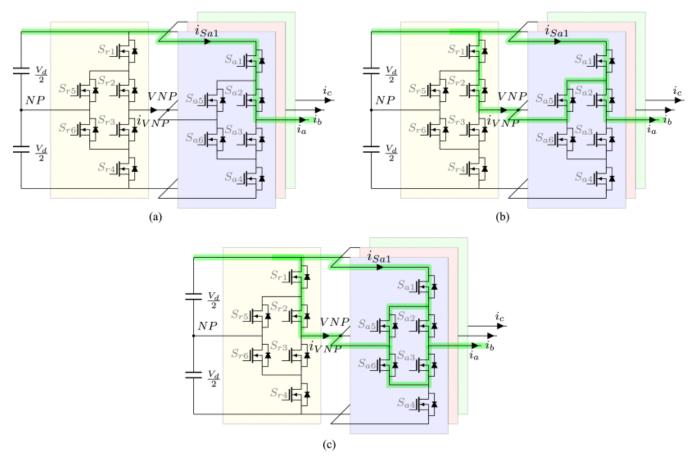

The topology of the fault-tolerant A3L-ANPC converter is shown in Fig. 1 . This converter consists of two parts, a conventional 3L-ANPC converter with three phase legs shown on the right and an additional fault-tolerant 3L-ANPC leg shown on the left. The additional 3L-ANPC leg enhances the converter's fault-tolerant effectiveness by compensating for faulty switches in the other three phase legs. The neutral point input to the fault-tolerant leg (on the left side of Fig. 1) will be referred as the neutral point (NP) while the neutral point input to the three phase legs (on the right side of Fig. 1) will be called as the virtual neutral point (VNP).

Table I shows the possible switching states for a typical phase leg and the fault-tolerant leg of the A3L-ANPC converter under normal operation. The subscript "a" refers to phase-A leg while the subscript "r" refers to the redundant fault-tolerant leg. The switching state selected decides the phase output potential. As it is obvious from Table I, there are several options for each of the major states P, O, and N.

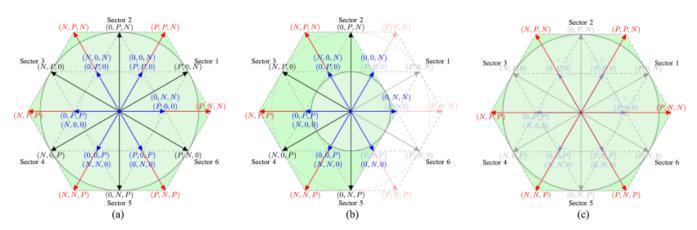

During normal operation, the inner switches of the fault-tolerant leg are constantly turned ON to connect the NP to the VNP. For example, the switching state for positive phase output P1 includes turning ON  $S_{a1}$  and  $S_{a2}$ , while the fault-tolerant leg is in a default state with  $S_{r2}$ ,  $S_{r3}$ ,  $S_{r5}$ , and  $S_{r6}$   $S_{r6}$  turned ON. The available voltage vectors in normal operation are depicted in Fig. 3(a). However, in fault-tolerant operation mode, the output of the fault-tolerant leg can be connected to the positive dc bus, the neutral point, or the negative dc bus depending on which device fault that will be compensated. The fault-tolerant compensation methods will be discussed in the following subsections. It should be noted that, considering the circuit symmetry of the proposed A3L-ANPC converter, only three devices on the Phase-A leg,  $(S_{a1}, S_{a2}, \text{ and } S_{a5})$ , will be investigated in this paper for open-circuit and short-circuit switching faults. Therefore, the fault behavior and the related fault-tolerant operation on other switching devices will not be repeated.

**Fig. 3.** Space vector diagrams of the A3L-ANPC converter. (a) Normal operation. (b)  $S_{a1}$  fails open. (c) Fault-tolerant operation.

## A. Open-Circuit Switch Faults

#### 1) Open-Circuit Switch Fault in $S_{a1}$

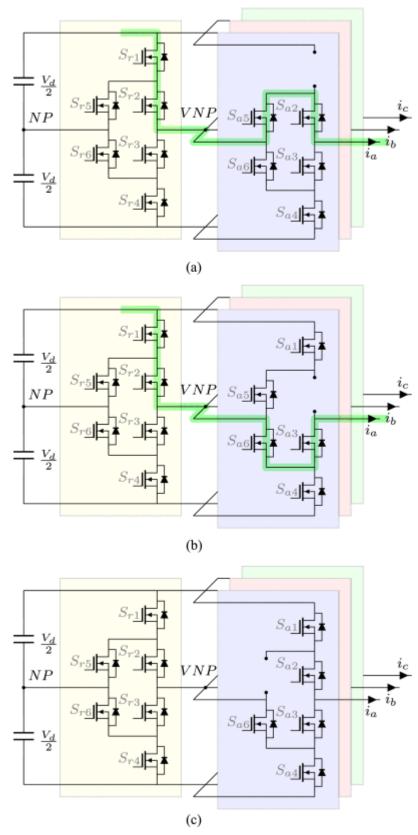

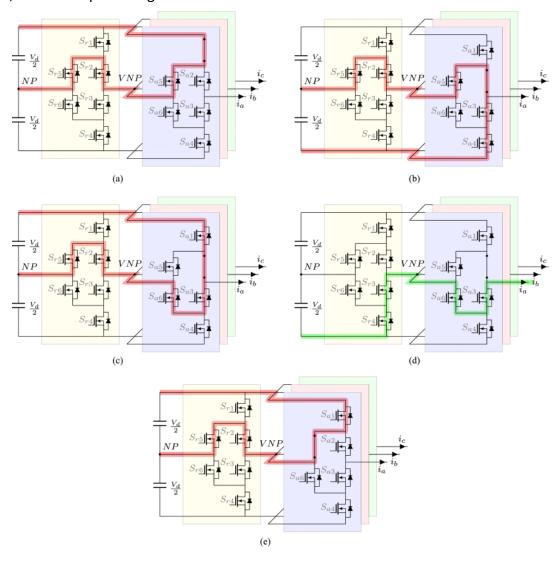

As shown in Table II, Phase-A cannot produce a positive voltage state (P) when there is an open-circuit fault in  $S_{a1}$ . This results in a reduction of the available output voltage vectors as shown in Fig. 3(b). Fig. 4(b) demonstrates a path that the fault-tolerant leg uses to compensate an open-circuit fault in in  $S_{a1}$ . To reclaim the missing states, P1 and P2, the switches  $S_{r1}$  and  $S_{r2}$  are turned ON to connect the positive dc-bus to the VNP. Meanwhile, as shown in Fig. 4(a), Phase-A leg has  $S_{a5}$  and  $S_{a2}$  turned ON providing a path from the VNP to the Phase-A output resulting in restoration of the lost state. Consequently, all O states are lost in all phases. Thereby, the converter can only output a full-scale two-level voltages, rather than three-level voltages, as indicated in Fig. 3(c).

**Fig. 4.** Fault-tolerant operation for various open-circuit device faults in the A3L-ANPC converter. (a)  $S_{a1}$  open-circuit fault. (b)  $S_{a2}$  open-circuit fault. (c)  $S_{a5}$  open-circuit fault.

TABLE II Fault-Tolerant Switching States at Different Open-Circuit Switch Faults in A3L-ANPC Converter

| Fault (Open | Lost States | Turn-on on    | Turn-on at fault-  | Output  |

|-------------|-------------|---------------|--------------------|---------|

| Circuit)    |             | Faulty Leg    | Tolerant Leg       | Voltage |

| $S_{a1}$    | P1          |               | P1                 | +Vd/2   |

|             | P2          | 0U1, 0U2, 0L2 | P2                 | +Vd/2   |

|             | 0L1         |               | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | P1          |               | P1                 | +Vd/2   |

| C           | P2          | 01.1.01.2     | P2                 | +Vd/2   |

| $S_{a2}$    | 0U1         | 0L1, 0L2      | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | 0U2         |               | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | N1          |               | N1                 | -Vd/2   |

| e .         | N2          | 0111 0112     | N2                 | -Vd/2   |

| $S_{a3}$    | 0L1         | 0U1, 0U2      | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | 0L2         |               | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | N1          |               | N1                 | -Vd/2   |

| $S_{a4}$    | N2          | 0U2, 0L1, 0L2 | N2                 | -Vd/2   |

|             | 0U1         |               | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | N2          |               | N2                 | -Vd/2   |

| $S_{a5}$    | 0U1         | 0L1, 0L2      | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | 0U2         |               | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | P2          |               | P2                 | +Vd/2   |

| $S_{a6}$    | 0L1         | 0U1, 0U2      | 0U1, 0U2, 0L1, 0L2 | 0       |

|             | 0L2         |               | 0U1, 0U2, 0L1, 0L2 | 0       |

One more switching state affected by the open-circuit fault in  $S_{a1}$  is the OL1 state. To compensate for the lost OL1 state, there are three other zero states available for use. Considering that switching back and forth between O and P state in the fault-tolerant leg will result in a sophisticated hybrid combination of three- and two-level waveforms, the fault-tolerant leg is simply used to retrieve P state to generate two-level output voltages.

#### 2) Open-Circuit Switch Fault in $S_{a2}$

During an open-circuit fault in  $S_{a2}$ , the output of Phase-A leg cannot produce a P state. Fig. 4(b) shows a path to retrieve the lost P state. To compensate for the missing P1 and P2 states, the switches  $S_{r1}$  and  $S_{r2}$  are turned ON to connect the positive dc-bus to the VNP. In Fig. 4(b), the faulty phase leg has  $S_{a3}$  and  $S_{a6}$  turned ON so that the VNP is connected to the phase output, thereby, restoring the lost state. Again, losing the ability to output zero in nonfaulty phase legs results in full-scale two-level voltages at the output, as illustrated in Fig. 3(c).

#### 3) Open-Circuit Switch Fault in $S_{a5}$

Fig. 4(c) shows an open-circuit fault in  $S_{a5}$ , which results in losing N2, OU1, and OU2 states. The alternative state for N2 is N1, and the zero states of OL1 and OL2 can be substituted with states OU1 and OU2. Under this fault scenario, full-scale three-level voltage output is retained.

#### B. Short-Circuit Switch Faults

#### 1) Short-Circuit Fault in $S_{a1}$

Fig. 5(a) shows the A3L-ANPC converter with a short-circuit fault in  $S_{a1}$ . Under normal operation the NP is connected to VNP to provide access to the neutral point. However, with a short-circuit fault in the switch  $S_{a1}$ , the switch  $S_{a5}$  must never be turned ON in order to avoid shoot-through between the positive dc-bus and the neutral point. In such scenario, the switching states, N2, OU1, and OU2, are lost, as shown in Table III. For the lost states of OU1 and OU2, the alternative states of OL1 and OL2 will be used. Similarly, for the lost state of N2, an alternative negative state N1 can be used instead. Therefore, the full output voltage can still be maintained in this fault scenario.

**Fig. 5.** Various short-circuit device faults in the ANPC converter. (a) Short-circuit path when turning ON the  $S_{a3}$  and  $S_{a4}$  while having a short-circuit fault in  $S_{a1}$ . (b) Short-circuit path when turning ON the  $S_{a5}$  while having a short-circuit fault in  $S_{a2}$ . (c) Short-circuit path when turning ON the  $S_{a1}$ ,  $S_{a3}$ , and  $S_{a6}$  while having a short-circuit

fault in  $S_{a2}$ . (d) Fault-tolerant operation to generate negative voltage while having a short-circuit fault in  $S_{a2}$ . (e) Short-circuit path when turning ON the  $S_{a1}$  to generate P or OL1 while having a short-circuit fault in  $S_{a5}$ .

TABLE III Fault-Tolerant Switching States at Different Short-Circuit Switch Faults in A3L-ANPC Converter

| Fault    | Lost  | Alternative      | Turn-on on         | Output  |

|----------|-------|------------------|--------------------|---------|

| (Short   | State | States on Faulty | Fault-Tolerant     | Voltage |

| Circuit) |       | leg              | leg                |         |

|          | N2    | N1               |                    | -Vd/2   |

| $S_{a1}$ | 0U1   | 0L1, 0L2         | 0U1, 0U2, 0L1, 0L2 | 0       |

|          | 0U2   | 0L1, 0L2         | 0U1, 0U2, 0L1, 0L2 | 0       |

| C        | N2    | N1               |                    | -Vd/2   |

| $S_{a2}$ | 0L1   | 0U1, 0U2, 0L2    | 0U1, 0U2, 0L1, 0L2 | 0       |

| G        | P2    | P1               |                    | +Vd/2   |

| $S_{a3}$ | 0U1   | 0U2, 0L1, 0L2    | 0U1, 0U2, 0L1, 0L2 | 0       |

|          | P2    | P1               |                    | +Vd/2   |

| $S_{a4}$ | 0L1   | 0U1, 0U2         | 0U1, 0U2, 0L1, 0L2 | 0       |

|          | 0L2   | 0U1, 0U2         | 0U1, 0U2, 0L1, 0L2 | 0       |

| G        | P2    | P1               |                    | +Vd/2   |

| $S_{a5}$ | 0L1   | 0U1, 0U2, 0L2    | 0U1, 0U2, 0L1, 0L2 | 0       |

| C        | N2    | N1               |                    | -Vd/2   |

| $S_{a6}$ | 0U1   | 0U2, 0L1, 0L2    | 0U1, 0U2, 0L1, 0L2 | 0       |

#### 2) Short-Circuit Fault in $S_{a2}$

In this case, the lost states are N1, N2, and OL1. Turning ON  $S_{a3}$  and  $S_{a4}$  in order to obtain one of the N states will result in a short-circuit in the path shown in Fig. 5(b). Turning ON  $S_{a1}$ ,  $S_{a3}$ , and  $S_{a6}$  in order to obtain OL1 will result in a short circuit and is depicted in Fig. 5(c). The alternative path to generate the N state for the fault-tolerant operation of the phase leg A is shown in Fig. 5(d). Retrieving the lost N states in this case will require the connection of the negative rail to VNP resulting in the loss of the O states in all phases. Thus, the converter can only output a full-scale two-level voltage for this fault scenario.

#### 3) Short-Circuit Fault in $S_{a5}$

A short-circuit fault at  $S_{a5}$  will result in losing states P1, P2, and OL1. Fig. 5(e) shows the short-circuit path when turning ON the switch  $S_{a1}$  to generate the switching states P or OL1, while having a short-circuit fault in the switch  $S_{a5}$ . In the fault-tolerant mode, the VNP is disconnected from the NP, subsequently the O state will be lost. Such remedial action isolates the faulty device, but the converter can only output a full-scale two-level voltage.

In summary, because of the symmetry of the converter topology,  $S_{a3}$ ,  $S_{a4}$ , and  $S_{a6}$  are dual fault scenarios of the discussed fault cases in  $S_{a1}$ ,  $S_{a2}$ , and  $S_{a5}$ , respectively, and thus, they are not going to be discussed in detail but are listed in Tables II and III.

#### SECTION IV.

#### **Experimental Verification**

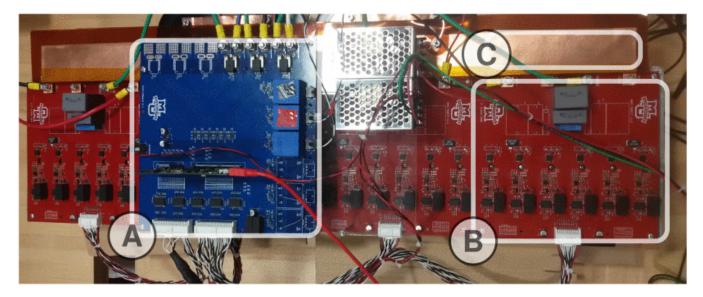

In order to validate the fault-tolerant capabilities of the A3L-ANPC converter topology, a 25-kW prototype was designed and implemented. The experimental setup is displayed in Fig. 6. The prototype is comprised of 24 SiC MOSFETs (Model No.: CREE C2M0025120D, rated at 1200V/60A). A digital signal processor (DSP) TMS320F28377D was used in the setup to control the converter. A three-phase RL load in wye configuration, with a resistance per phase of 10  $\Omega$  and inductance per phase of 900  $\mu$  H, was connected to the output of the converter. The dc-bus voltage is 1 kV and the nominal output power in the test is 25 kW. The switching frequency was set at 10 kHz. Finally, the fundamental output frequency and the modulation index were set at 60 Hz and 0.8, respectively.

**Fig. 6.** Experimental prototype of the customized A3L-ANPC converter: (A) control board, (B) Phase-A leg, (C) dc-bus bar.

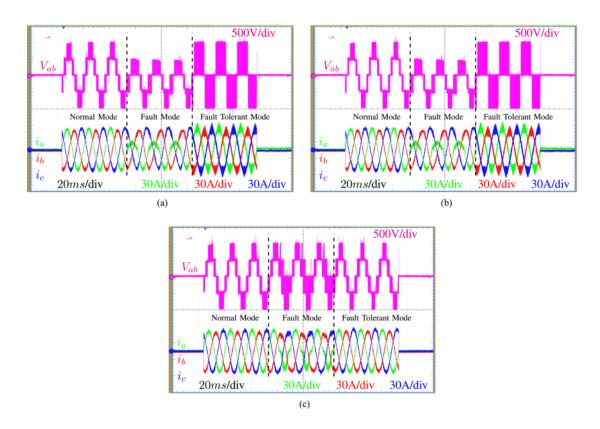

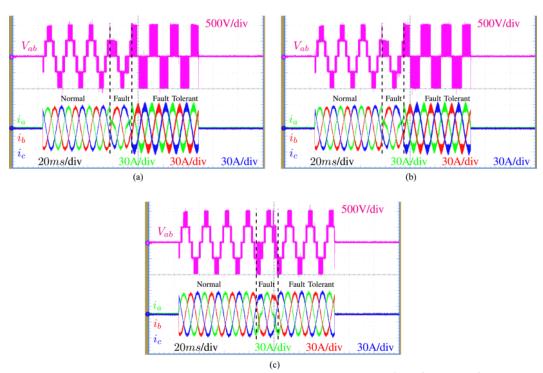

In the experimental results presented later for both switch open-circuit and short-circuit fault tests, the A3L-ANPC converter was programmed to output three cycles of normal operation, followed by three cycles of faulty operation, and finally, three cycles of fault-tolerant operation. This is in order to show the variations of the line-to-line voltages and phase currents under normal operation, faulty operation, and fault-tolerant operation. The experimental results for verifying the fault-tolerant operations of various open-circuit device faults in the A3L-ANPC converter are shown in Fig. 7. Fig. 7(a) depicts an open-circuit fault in  $S_{a1}$ . The first three cycles of the line-to-line voltage and three-phase currents are in normal operation. The second three cycles illustrate an open-circuit fault in  $S_{a1}$ , in which the output voltage cannot reach the full scale of dc-bus voltage (i.e., 1 kV). This indicates the loss of the P state in the Phase-A leg. The last three cycles exhibit the line-to-line voltage and three-phase currents during

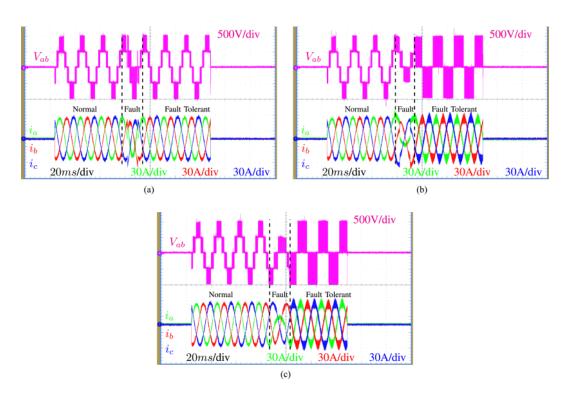

fault-tolerant operation mode, which exhibits two-level voltage waveforms since the converter is modulated as a two-level converter, but the full modulation index is retained. In addition, it can be seen that the line-to-line voltage and current waveforms exhibit more harmonics during fault-tolerant mode because of the two-level operation of the converter. The similar observation can be applied to the fault-tolerant operation for the open-circuit fault in  $S_{a2}$ , which is shown in Fig. 7(b). However, for an open-circuit switch fault in the switch  $S_{a5}$ , shown in Fig. 7(c), the A3L-ANPC converter can still output a three-level waveform without any derating, and thus, the phase currents remain unchanged with no increase in harmonic distortion. The experimental results for short-circuit faults in devices,  $S_{a1}$ ,  $S_{a2}$ ,  $S_{a5}$ , are demonstrated in Fig. 8(a)–(c), respectively. Since these waveforms are similar to the results for open-circuit device faults, explanations will not be repeated here.

**Fig. 7.** Measured line-to-line voltages and currents during healthy operation (the first set of three cycles), open-circuit faulty operation (the second set of three cycles), and fault-tolerant operation (the third set of three cycles) of the A3L-ANPC converter. Ch1 (blue) 30 A/div, Ch2 (red) 30 A/div, Ch3 (green) 30 A/div, and Ch4 (magenta) 500 V/div. (a) Open-circuit fault in  $S_{a1}$ . (b) Open-circuit fault in  $S_{a2}$ .

**Fig. 8.** Measured line-to-line voltages and currents during healthy operation (the first set of three cycles), short-circuit faulty operation (the second set of three cycles), and fault-tolerant operation (the third set of three cycles) of the A3L-ANPC converter. Ch1 (blue) 30 A/div, Ch2 (red) 30 A/div, Ch3 (green) 30 A/div, and Ch4 (magenta) 500 V/div. (a) Short-circuit fault in  $S_{a1}$ . (b) Short-circuit fault in  $S_{a2}$ .

It should be noted that showing the three faulty cycles in this paper is for illustration purpose and it is exaggerated. Adopting a fault detection technique will claim the fault-tolerant operation much more faster. This paper is not considering the investigation on the fault detection method. Therefore, for preventing a shoot through in lower dc-link capacitor during a short circuit fault at  $S_{a2}$  [as shown in Fig. 5(b)], the  $S_{a4}$  is intentionally turned OFF. Turning OFF the  $S_{a4}$  will result in losing the N state, which is shown in the three faulty cycles of Fig. 8(b). This faulty state is shown in three cycles to show the effect of losing the N state on the output voltage. The mechanism that triggers the fault detection technique is the short-circuit fault feedback in the system. Since the semiconductors used in the A3L-ANPC converter are SiC MOSFETs the short-circuit detection mechanism should be able to turn OFF the short-circuit fault in less than 5  $\mu$ s.

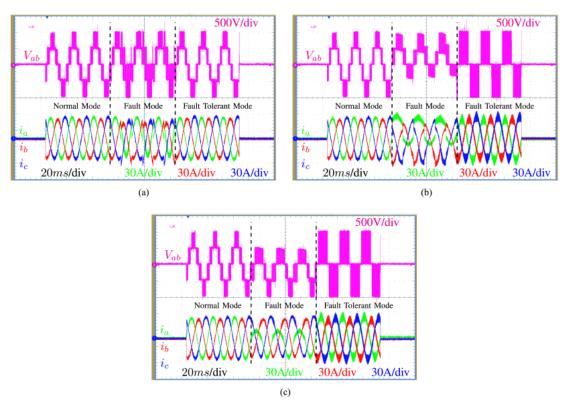

In order to further investigate the fault-tolerant capability of the A3L-ANPC converter, the open-circuit fault in  $S_{a1}$  and  $S_{a2}$  is introduced in the positive peak of  $i_a$  as shown in Fig. 9(a) and (b), respectively. Fig. 9(c) demonstrates the open-circuit fault introduced in negative peak of the  $i_a$ . The fault duration is lasting for one cycle deliberately for illustration purposes. Similar conditions as open-circuit fault are applied to short-circuit tests, which are shown in Fig. 10(a)–(c) .

**Fig. 9.** Measured line-to-line voltages and currents during healthy operation (the first set of three cycles), open-circuit faulty operation (the second set of one cycle), and fault-tolerant operation (the third set of three cycles) of the A3L-ANPC converter. Ch1 (blue) 30 A/div, Ch2 (red) 30 A/div, Ch3 (green) 30 A/div, and Ch4 (magenta) 500 V/div. (a) Open-circuit fault in  $S_{a1}$ . (b) Open-circuit fault in  $S_{a2}$ .

**Fig. 10.** Measured line-to-line voltages and currents during healthy operation (the first set of three cycles), short-circuit faulty operation (the second set of one cycle), and fault-tolerant operation (the third set of three cycles) of the A3L-ANPC converter. Ch1 (blue) 30 A/div, Ch2 (red) 30 A/div, Ch3 (green) 30 A/div, and Ch4 (magenta) 500 V/div. (a) Short-circuit fault in  $S_{a1}$ . (b) Short-circuit fault in  $S_{a2}$ . (c) Short-circuit fault in  $S_{a5}$ .

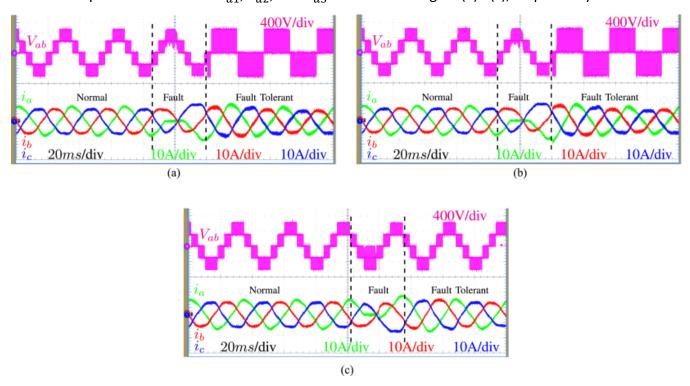

To investigate the fault-tolerant operation of the A3L-ANPC converter in specific applications such as a motor-drive system, the converter is connected to a 3-kW induction motor-generator setup. The test results for open-circuit faults in  $S_{a1}$ ,  $S_{a2}$ , and  $S_{a5}$  are shown in Fig. 11(a)— (c), respectively.

Fig. 11. Measured line-to-line voltages and currents during healthy operation (the first set of three cycles), short-circuit faulty operation (the second set of one cycle), and fault-tolerant operation (the third set of three cycles) of the A3L-ANPC converter feeding a 3-kW induction motor-generator setup. Ch1 (blue) 10 A/div, Ch2 (red) 10 A/div, Ch3 (green) 10 A/div, and Ch4 (magenta) 400 V/div. (a) Open-circuit fault in  $S_{a1}$ . (b) Open-circuit fault in  $S_{a2}$ . (c) Open-circuit fault in  $S_{a5}$ .

#### SECTION V.

## Current Sharing Capabilities of the A3L-ANPC Converter

The current sharing characteristics of the A3L-ANPC converter is achieved by leveraging the redundant leg that can increase the overload capability and overall performance of the converter. Specifically, the redundant leg can be utilized to share the load current with three main phase legs under normal operating conditions. Current sharing capability is very beneficial in reducing the thermal stress in the outer switches ( $S_{x1}$  and  $S_{x4}$ , where x=a, b, or c). Particularly, the outer switches in the converter have the largest thermal stress under the conditions of unity power factor and maximum modulation index [6]. However, it should be clarified that current sharing between the redundant leg and the three phase legs is only available at the six large voltage vectors.

#### A. Current Sharing in Three-Level Mode

The large space vectors include P states and N states solely and the medium vectors and small vectors include at least one O state. Therefore, the redundant leg can output a P state or N state in the interest of sharing the current.

If the redundant leg outputs a P state or N state while another phase leg requires a O state, a dc-bus short-circuit fault may occur. To avoid a shoot-through fault, the redundant leg can only share current when large space vectors are used.

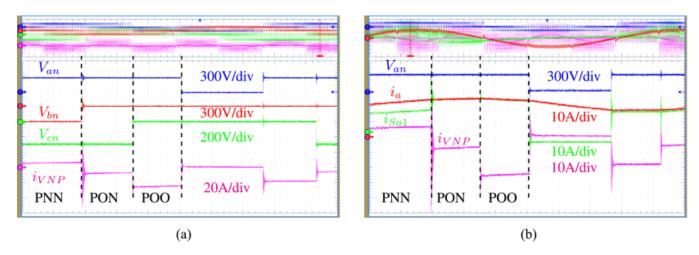

For instance, at the switching state of (P, N, N), the switches  $S_{r1}$  and  $S_{r2}$  on the redundant leg can be turned ON to share the positive load current with the Phase-A leg, as shown in Fig. 13(b). This capability is verified by the experimental results given in Fig. 13(a) and (b). In Fig. 13(a), the three line-to-neutral voltages,  $V_{an}$ ,  $V_{bn}$ , and  $V_{cn}$ , show the switching states of (P, N, N) and (P, O, N). Under the same operating condition, the load current sharing between the redundant leg and the Phase-A leg is demonstrated in Fig. 13(b). It should be noted that the total load current is shared by the current flowing through  $S_{r1}$  and  $S_{a1}$  at the switching state (P, N, N). However, at the switching state (P, O, N), the current sharing strategy has to be disabled due to the necessity of using the redundant leg to output zero voltage for Phase-B leg. This is also shown in Fig. 13(b) where the load current equals the current flowing through  $S_{a1}$ . It should be pointed out that the current through  $S_{r1}$  is represented by  $I_{VNP}$  in Fig. 13(b). The similar current sharing strategy can be implemented for the other five large vectors, and will not be repeated here.

In order to further reduce the device conduction losses during current sharing mode, the lower neutral path of the A3L-ANPC converter can be turned ON after the upper neutral path is turned ON, as is shown in Fig. 12(c). First the upper neutral path is turned ON to build up the shared current, and then, the lower neutral path is turned ON to provide a quasi-zero-voltage soft switching for the lower neutral path. Assuming the on-state resistance of each SiC MOSFET as R, the resultant on-state resistance between the positive dc bus and the Phase-A output terminal will be 2R when there is no current sharing as shown in Fig. 12(a). Accordingly, the on-state resistance between the positive dc-bus and the output terminal would be 1.75R and 1.33R with different current sharing schemes as shown in Fig. 12(b) and (c), respectively. Obviously, using the redundant leg for sharing the load current in normal operation can reduce the conduction losses significantly.

**Fig. 12.** Current sharing capability in A3L-ANPC converter topology. (a) No current sharing path for Phase-A. (b) Current sharing path for Phase-A. (c) Improved current sharing path for Phase-A.

**Fig. 13.** Current sharing capability in A3L-ANPC converter topology, time base 2 ms/div. (a) Phase voltages. (b) Shared currents.

#### **B. Current Sharing in Two-Level Mode**

The current sharing characteristic of the A3L-ANPC converter can be utilized exclusively if the converter is operated only with large space vectors. In other words, the three-level A3L-ANPC converter has to be modulated as a two-level converter, which is possible in normal operation or fault-tolerant operation.

However, the drawback of this mode is the increased harmonics in the output voltages. If two-level mode is sufficient for the application, current sharing in two-level mode can be utilized for overload, startup, and stall conditions.

#### SECTION VI.

#### Comparison and Cost Justification

A comparison of the fault-tolerant capability between the introduced A3L-ANPC converter and the conventional 3L-ANPC converters is summarized in Tables IV and V. It can be seen from these tables that the A3L-ANPC converter can operate at full power under any single device fault condition. In contrast, the conventional 3L-ANPC converter can only operate in a derated mode during a single device open-circuit fault in switches  $S_{a1} - S_{a4}$  [10]. For an open-circuit fault, the modulation index for the A3L-ANPC converter can be maintained at  $2/\sqrt{3}$  as shown in Table IV.

**TABLE IV** Open-Circuit Fault Comparison Table

| Fault                  | Conventional 3L-ANPC half rated | Conventional 3L-ANPC full rated | Proposed<br>A3L-ANPC  |  |

|------------------------|---------------------------------|---------------------------------|-----------------------|--|

| $S_{a1}$               | Lose P                          | Lose P                          | Recover               |  |

|                        | half modulation index           | half modulation index           | full modulation index |  |

| $S_{a2}$               | Lose P                          | Lose P                          | Recover               |  |

| Daz                    | half modulation index           | half modulation index           | full modulation index |  |

| $S_{a3}$               | Lose N                          | Lose N                          | Recover               |  |

| Das                    | half modulation index           | half modulation index           | full modulation index |  |

| $S_{a4}$               | Lose N                          | Lose N                          | Recover               |  |

| Da4                    | half modulation index           | half modulation index           | full modulation index |  |

| $S_{a5}$               | Lose Upper O                    | Lose Upper O                    | Recover               |  |

| Das                    | Recover                         | Recover                         | full modulation index |  |

| $S_{a6}$               | Lose Lower O                    | Lose Lower O                    | Recover               |  |

| <i>S</i> <sub>a6</sub> | Recover                         | Recover                         | full modulation index |  |

**TABLE V** Short-Circuit Fault Comparison Table

| Fault    | Conventional 3L-ANPC half rated | Conventional 3L-ANPC full rated | Proposed<br>A3L-ANPC  |  |

|----------|---------------------------------|---------------------------------|-----------------------|--|

| S .      | Lose N                          | Recover                         | Recover               |  |

| $S_{a1}$ | half modulation index           | full modulation index           | full modulation index |  |

| $S_{a2}$ | Lose N                          | Recover                         | Recover               |  |

| $S_{a2}$ | half modulation index           | full modulation index           | full modulation index |  |

| $S_{a3}$ | Lose P                          | Recover                         | Recover               |  |

| $D_{a3}$ | half modulation index           | full modulation index           | full modulation index |  |

| $S_{a4}$ | Lose P                          | Recover                         | Recover               |  |

| Da4      | half modulation index           | full modulation index           | full modulation index |  |

| $S_{a5}$ | Lose P                          | Lose P                          | Recover               |  |

| $S_{a5}$ | half modulation index           | half modulation index           | full modulation index |  |

| $S_{a6}$ | Lose N                          | Lose N                          | Recover               |  |

| Sa6      | half modulation index           | half modulation index           | full modulation index |  |

Recovering from short-circuit faults in the 3L-ANPC converter is dependent on the ratings of the semiconductor devices used in the topology. As shown in Table V, a 3L-ANPC converter can recover from more short-circuit faults if the semiconductors are rated at full dc-bus voltage. Although the rating of the semiconductors in the conventional 3L-ANPC converter can make a difference in recovering from short-circuit faults, it is still impossible to recover from all short-circuit faults in the 3L-ANPC converter. However, with voltage ratings of full dc-bus voltage, the proposed A3L-ANPC converter can recover from all short-circuit faults with full modulation index.

The semiconductors in A3L-ANPC are rated at full dc-bus voltage. This choice is different from the conventional 3L-ANPC converter where the semiconductor devices typically are rated at half dc-bus voltage. However, the cost for fully rated semiconductors in an A3L-ANPC converter is justified in applications where fault tolerance and reliability is paramount. Moreover, using the current sharing scheme in Fig. 12(c) that enables a significant reduction of the conduction loss is only possible if the semiconductors are rated at full dc-bus voltage.

The voltage rating of the semiconductor devices on the redundant leg are also considered to be able to tolerate the full dc-bus voltage. In normal operation, these semiconductor devices can survive if they are sized at half of the dc-bus voltage. However, in fault-tolerant operation, there are certain cases that the devices must be able to tolerate the full dc-bus voltage in order to survive from the fault. The current rating of the semiconductor devices on the redundant leg will be sized as the same as these on the main phase legs. This is because of the fact that the devices on the redundant leg will interface the rated current of the converter in some open-circuit fault scenarios, as discussed in previous sections.

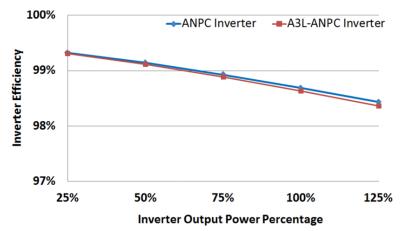

To evaluate the efficiency of the proposed A3L-ANPC converter, thermal modeling and simulation were carried out in PLECS software. The simulation conditions are given in Table VI. In the thermal simulation of the A3L-ANPC converter, the four middle SiC MOSFETs in the redundant phase leg, namely,  $S_{r2}$ ,  $S_{r3}$ ,  $S_{r5}$ , and  $S_{r6}$ , are kept constant ON. Therefore, there are no switching losses in these middle switches, and their conduction losses during operation are marginal due to the current sharing by the two parallel conduction paths constituted by the upper path  $(S_{r2})$  and  $(S_{r3})$  and lower path  $(S_{r3})$ and  $S_{r6}$ ). A comparison of the converter efficiency between the conventional ANPC inverter and the proposed A3L-ANPC converter under the same conditions is shown in Fig. 14. As it can be seen, for the output power below the rated power of 25 kW, the proposed A3L-ANPC converter has almost the same efficiency as that of the conventional ANPC converter. At rated output power condition (100% output power), the efficiency of the proposed SiC A3L-ANPC converter is only 0.05% lower than the conventional SiC ANPC converter, which results from the conduction losses of the middle switches ( $S_{r2}$ ,  $S_{r3}$ ,  $S_{r5}$ , and  $S_{r6}$ ). At 125% overload conditions (i.e., 1.25 times higher than the rated converter power), the efficiency of the A3L-ANPC converter is only 0.07% lower than the conventional SiC ANPC converter. Therefore, one can conclude that this proposed A3L-ANPC converter can maintain approximately the same efficiency as the conventional ANPC converter while possess fault-tolerant capability to any open-circuit and certain short-circuit switching faults.

**Fig. 14.** Efficiency comparison between the proposed A3L-ANPC converter and the conventional ANPC converter.

**TABLE VI** Simulation Conditions for Efficiency Evaluation of the A3L-ANPC and Conventional ANPC Converters

| Parameter                                             | Value | Unit  |

|-------------------------------------------------------|-------|-------|

| Rated Power                                           | 25    | kW    |

| Rated DC-Bus Voltage                                  | 1000  | Volts |

| Fundamental Output Frequency                          | 60    | Hz    |

| Switching Frequency                                   | 10    | kHz   |

| Modulation Index                                      | 0.8   | N/A   |

| Power Factor                                          | 0.8   | N/A   |

| Ambient Temperature                                   | 50    | °C    |

| Junction-to-Case Thermal Resistance of the SiC MOSFET | 0.24  | °C/W  |

| Case-to-Sink Thermal Resistance of the SiC MOSFET     | 0.02  | °C/W  |

#### **SECTION VII.**

#### Conclusion

This paper introduces a novel fault-tolerant topology based on the conventional 3L-ANPC converter. According to the experimental results, this proposed A3L-ANPC converter possesses superior fault-tolerant capabilities compared to the conventional 3L-ANPC converter. The enhanced fault-tolerant capability is based on the addition of an identical ANPC phase leg. Moreover, under normal operation or faulty operation, the redundant leg in the A3L-ANPC converter can be utilized to share the current with other phase legs, which is beneficial for mitigating the thermal stress on outer switches in the converter. The experimental results show that the A3L-ANPC converter can operate without reduced output voltage and power under any device open-circuit or short-circuit fault. The current sharing between the redundant leg and other phase legs is also experimentally verified. This novel fault-tolerant multilevel converter topology can be used in safety-critical applications where the reliability of the power conversion system has a higher priority than the system cost.

#### References

- . J. Rodriguez, J.-S. Lai, F. Z. Peng, "Multilevel inverters: A survey of topologies controls and applications", *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724-738, Aug. 2002.

- . A. Nabae, I. Takahashi, H. Akagi, "A new neutral-point-clamped PWM inverter", *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518-523, Sep. 1981.

- . J. Rodriguez, S. Bernet, P. K. Steimer, I. E. Lizama, "A survey on neutral-point-clamped inverters", *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219-2230, Jul. 2010.

- . P. M. Bhagwat, V. Stefanovic, "Generalized structure of a multilevel PWM inverter", *IEEE Trans. Ind. Appl.*, vol. IA-19, no. 6, pp. 1057-1069, Nov. 1983.

- 5. B. Wu, High-Power Converters and AC Drives, New York, NY, USA:Wiley, 2006.

- . T. Bruckner, S. Bernet, H. Guldner, "The active NPC converter and its loss-balancing control", *IEEE Trans. Ind. Electron.*, vol. 52, no. 3, pp. 855-868, Jun. 2005.

- . S. Li, L. Xu, "Strategies of fault tolerant operation for three-level PWM inverters", *IEEE Trans. Power Electron.*, vol. 21, no. 4, pp. 933-940, Jul. 2006.

- . J. S. Lee, K. B. Lee, "Open-circuit fault-tolerant control for outer switches of three-level rectifiers in wind turbine systems", *IEEE Trans. Power Electron.*, vol. 31, no. 5, pp. 3806-3815, May 2016.

- . H. B. Abdelghani, A. B. B. Abdelghani, F. Richardeau, J. M. BlaquiÃre, F. Mosser, I. Slama-Belkhodja, "Fault tolerant-topology and controls for a three-level hybrid neutral point clamped-flying capacitor converter", *IET Power Electron.*, vol. 9, no. 12, pp. 2350-2359, 2016.

- . J. Li, A. Huang, Z. Liang, S. Bhattacharya, "Analysis and design of active NPC (ANPC) inverters for fault-tolerant operation of high-power electrical drives", *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 519-533, Feb. 2012.

- **11**. S. Ceballos et al., "Three-level converter topologies with switch breakdown fault-tolerance capability", *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 982-995, Mar. 2008.

- . S. Ceballos, J. Pou, E. Robles, J. Zaragoza, J. L. Martin, "Performance evaluation of fault-tolerant neutral-point-clamped converters", *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2709-2718, Aug. 2010.

- **13**. J. He, N. Weise, L. Wei, N. A. O. Demerdash, "A fault-tolerant topology of t-type NPC inverter with increased thermal overload capability", *Proc. 2016 IEEE Appl. Power Electron. Conf. Expo.*, pp. 1065-1070, Mar. 2016.

- **14**. P. Lezana, J. Pou, T. A. Meynard, J. Rodriguez, S. Ceballos, F. Richardeau, "Survey on fault operation on multilevel inverters", *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2207-2218, Jul. 2010.

- **15**. B. Mirafzal, "Survey of fault-tolerance techniques for three-phase voltage source inverters", *IEEE Trans. Ind. Electron.*, vol. 61, no. 10, pp. 5192-5202, Oct. 2014.

- **16**. J. He, N. A. O. Demerdash, N. Weise, R. Katebi, "A fast on-line diagnostic method for open-circuit switch faults in SiC-MOSFET-based T-type multilevel inverters", *IEEE Trans. Ind. Appl.*, vol. 53, no. 3, pp. 2948-2958, May 2017.

- **17**. J. He, R. Katebi, N. Weise, N. A. O. Demerdash, L. Wei, "A fault-tolerant T-type multilevel inverter topology with increased overload capability and soft-switching characteristics", *IEEE Trans. Ind. Appl.*, vol. 53, no. 3, pp. 2826-2839, May 2017.

- **18**. J. He, N. Weise, R. Katebi, L. Wei, N. Demerdash, "A fault-tolerant T-type multilevel inverter topology with soft-switching capability based on si and sic hybrid phase legs", *Proc. 2016 IEEE Energy Convers. Congr. Expo.*, pp. 1-7, Sep. 2016.

- **19**. J. He, N. A. O. Demerdash, "An on-line diagnostic method for open-circuit switch faults in NPC multilevel converters", *Proc. 2016 IEEE Energy Convers. Congr. Expo.*, pp. 1-7, Sep. 2016.

- 20. J. He, "Health condition monitoring and fault tolerant operation of adjustable speed drives", 2015.

- **21**. T. Krone, C. Xu, A. Mertens, "Fast and easily implementable detection circuits for short circuits of power semiconductors", *IEEE Trans. Ind. Appl.*, vol. 53, no. 3, pp. 2871-2879, May 2017.

- **22**. R. Katebi, A. Stark, J. He, N. Weise, "Advanced three level active neutral point converter with fault tolerant capabilities", *Proc. 2016 IEEE Energy Convers. Congr. Expo.*, pp. 1-7, Sep. 2016.