#### Marguette University

# e-Publications@Marquette

**Electrical and Computer Engineering Faculty** Research and Publications

Electrical and Computer Engineering, Department of

3-2019

# A Bidirectional Soft-Switched DAB-Based Single-Stage Three-Phase AC-DC Converter for V2G Application

Dibaker Das Indian Institute of Science

Nathan Weise Marquette University, nathan.weise@marquette.edu

Kaushik Basu Indian Institute of Science

Rohit Baranwal MTS Systems Corporation

Ned Mohan University of Minnesota

Follow this and additional works at: https://epublications.marguette.edu/electric\_fac

Part of the Computer Engineering Commons, and the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Das, Dibaker; Weise, Nathan; Basu, Kaushik; Baranwal, Rohit; and Mohan, Ned, "A Bidirectional Soft-Switched DAB-Based Single-Stage Three-Phase AC-DC Converter for V2G Application" (2019). Electrical and Computer Engineering Faculty Research and Publications. 616.

https://epublications.marquette.edu/electric\_fac/616

#### **Marquette University**

# e-Publications@Marquette

# Electrical and Computer Engineering Faculty Research and Publications/College of Engineering

This paper is NOT THE PUBLISHED VERSION; but the author's final, peer-reviewed manuscript. The published version may be accessed by following the link in the citation below.

*IEEE Transactions on Transportation Electrification*, Vol. 5, No. 1 (March 2019): 186-199. <u>DOI</u>. This article is © Institute of Electrical and Electronic Engineers (IEEE) and permission has been granted for this version to appear in <u>e-Publications@Marquette</u>. Institute of Electrical and Electronic Engineers (IEEE) does not grant permission for this article to be further copied/distributed or hosted elsewhere without the express permission from Institute of Electrical and Electronic Engineers (IEEE).

# A Bidirectional Soft-Switched DAB-Based Single-Stage Three-Phase AC—DC Converter for V2G Application

#### Dibakar Das

Department of Electrical Engineering, Indian Institute of Science, Bengaluru, India

#### Nathan Weise

Department of Electrical and Computer Engineering, Marquette University, Milwaukee, WI

#### Kaushik Basu

Department of Electrical Engineering, Indian Institute of Science, Bengaluru, India

#### **Rohit Baranwal**

MTS Systems Corporation, Eden Prairie, MN

#### **Ned Mohan**

Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN

#### Abstract:

In vehicle-to-grid applications, the battery charger of the electric vehicle (EV) needs to have a bidirectional power flow capability. Galvanic isolation is necessary for safety. An ac-dc bidirectional power converter with high-frequency isolation results in high power density, a key requirement for an on-board charger of an EV. Dual-active-bridge (DAB) converters are preferred in medium power and high voltage isolated dc-dc converters due to high power density and better efficiency. This paper presents a DAB-based three-phase ac-dc isolated converter with a novel modulation strategy that results in: 1) single-stage power conversion with no electrolytic capacitor, improving the reliability and power density; 2) open-loop power factor correction; 3) soft-switching of all semiconductor devices; and 4) a simple linear relationship between the control variable and the transferred active power. This paper presents a detailed analysis of the proposed operation, along with simulation results and experimental verification.

#### **Index Terms**

Dual active bridge (DAB), high-frequency link, single-stage ac-dc converter, soft-switching.

#### **SECTION I. Introduction**

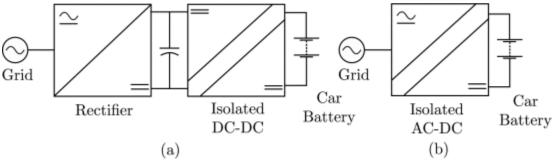

There is a growing interest toward the development of converters for hybrid electric vehicle (EV) charging systems due to increasing awareness about global warming [1]. Hybrid EV chargers can be broadly classified into two groups: on-board and off-board chargers. On-board chargers have the necessary power electronics on the vehicle to enable charging from a conventional utility power outlet. Typical power level of an on-board charger is limited to a few tens of kilowatts by size and weight constraints. The on-board charger system must be highly efficient and must have high power density and reliability. For vehicle-to-grid (V2G) applications, the charger must be able to support bidirectional power flow [2], [3]. Conventional EV chargers at this power level have two-stage architecture as shown in Fig. 1(a), which uses an ac–dc rectifier followed by an isolated dc–dc converter [4], [5]. The ac–dc converter is modulated to draw sinusoidal grid currents. The dc–dc converter is used for voltage matching and providing isolation at high frequency, which results in transformer size reduction. In this topology, an electrolytic capacitor is used to support the intermediate dc link, which reduces the reliability of the overall system. Moreover, multiple stages of power conversion reduce the overall power density of the system.

Fig. 1. (a) Typical power architecture of a two stage battery charger. (b) Conceptual diagram of the proposed single-stage battery charger.

The relative drawbacks of multistage topologies have led to the development of single-stage topologies which transfer active power without any intermediate stage. They have a better power density and reliability due to the exclusion of the dc link electrolytic capacitor [6]. Several single-stage-isolated EV charger topologies have been proposed in [7]–[8][9]. The focus of this paper is on a single-stage three-phase-isolated ac–dc converter.

The proposed modulation strategy is based on dual-active-bridge (DAB) principle that meets the essential requirements of an on-board EV charger.

DAB-based dc—dc power converter was proposed in [10]. This type of power conversion is suited for high voltage and medium power applications where isolation is required and high power density is important [5], [11], [12]. Two single-phase full-bridge converters are operated in square-wave modulation with a phase shift to transfer active power.

Later, it was found that one can also control the duty cycle of the two square waves by introducing zero states. Therefore, in total, there are three degrees of freedom: two duty cycles and the phase shift. A large body of literature exists that tries to answer the following question: For a given active power, how to set these three degrees of freedom so that rms of the winding currents or the conduction loss in the bridges and transformer can be minimized while satisfying the soft-switching conditions [13]–[14][15][16]. Some authors aimed at the minimization of the reactive component of power, which is closely related to the conduction loss [17]–[18][19].

DAB-based single-stage single-phase ac—dc converters have been discussed in [20]–[21][22][23]. In [21], a modulation strategy is proposed, which achieves open-loop power factor correction and soft-switching. An extension of the modulation strategy has been discussed in [22]. In [23], a variable switching frequency-based modulation strategy has been proposed. The DAB-based ac—dc converters described in [24] employs a line frequency switched rectifier followed by DAB converter stage. The intermediate dc input to the DAB converter is the rectified version of the line frequency ac.

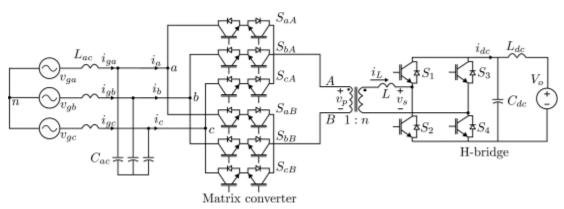

DAB-based single-stage three-phase converters have been discussed in [25]–[26][27][28], where [25] supports unidirectional power flow. A single-stage reduced switch count converter is proposed in [26], where the ac-ac converter on primary is realized using a push-pull structure. This paper presents a space vector modulation strategy for the DAB converter. Soft-switching analysis in this paper shows that the primary side switches do not receive soft-switching for most of the operating modes, whereas one of the transitions in the secondary bridge is partially hard-switched. The two switches in the primary have high rms and peak current rating. Different modulation strategies based on the topology shown in Fig. 2 have been proposed in [27] and [28]. In [27], the dc-side H-bridge is operated with square-wave modulation and a quasi-square wave is applied from the ac side with the max and the mid ac line-line voltage. The HF inductor current is assumed to be a square waveform for the determination of duty cycles of the primary voltages and the power. This results in low-frequency harmonics on the ac input current waveform. A soft-switching analysis is presented. However, ensuring proper current polarities which gives soft-switching over the entire line cycle is not discussed. A modulation strategy that alleviates the low-frequency harmonic problem is described in [28]. The ac-side matrix converter (MC) is used to apply sequentially two square waveforms formed by the max and mid ac line-line voltages. A phase-shifted square waveform is applied from the secondary for each of the square waveform applied from the primary. Although the low-frequency harmonic problem is addressed, this paper does not discuss soft-switching.

A three-phase single-stage DAB-based ac—dc converter as shown in Fig. 2 was proposed in [29]. This paper discusses a modulation strategy achieving input power factor correction and soft-switching. The proposed modulation strategy is an extension of the modulation scheme proposed in [21]. However, no detailed analysis and experimental results have been provided. In this paper, a DAB-based modulation strategy has been proposed for the converter shown in Fig. 2 that results in: 1) loss-less switching: zero-current switching [zero current switching (ZCS)] in the ac-side bridge and zero voltage switching in the dc-side bridge; 2) open-loop input power factor correction without dc-side load current sensing; and 3) a simplified plant for closed-loop control, as the phase shift or control input is proportional to the transferred active power.

This paper is organized in four sections. After the introduction in Section I, Section II describes the analysis of the proposed modulation for the converter over a switching period and from that derives the line frequency quantities for dc power transferred and rms current in the transformer windings. The design procedure of the converter and filter is discussed in detail. A detailed analysis on soft-switching of the converter has been provided. Section III contains simulation and experimental results showing the operation of the proposed modulation and Section IV concludes this paper.

## SECTION II. Analysis

This section presents the proposed modulation scheme, derivation of closed-form expressions of important quantities such as dc power transferred and soft-switching mechanism. The topology of the converter is shown in Fig. 2. The ac-side converter, the left side of Fig. 2, is comprised of six four-quadrant switches  $[[S_{aA} - S_{cB}]]$ . They are realized using two emitter tied IGBT's with their respective antiparallel diodes. These switches create a three-phase to single-phase MC. The single-phase side of the MC is connected to the primary winding of a single-phase high-frequency transformer (HFT). The ac input side has a low-pass LC filter ( $C_{ac}$  and  $L_{ac}$ ) between the source and the three-phase to single-phase MC to suppress current harmonics drawn from the grid. The turns ratio of the single-phase transformer is 1:n. In this analysis, the magnetizing inductance, winding resistance, and core losses are neglected. The primary and secondary leakage inductances are lumped together on the secondary as L. The secondary of the single-phase transformer is connected to a H-bridge converter comprised of four two-quadrant switches  $[S_1 - S_4]$ . The current on the dc side of the converter is filtered with an LC filter ( $C_{dc}$  and  $L_{dc}$ ). Finally, the H-bridge is connected to a dc source of voltage  $V_o$ . In the following analysis, all switches are considered ideal.

#### A. Modulation

#### 1) Input Voltages:

For analyzing the modulation of the converter, it is assumed that the filter inductance  $L_{\rm ac}$  offers negligible impedance at line frequency. Thus, the utility voltages  $v_{ga}$ ,  $v_{gb}$ , and  $v_{gc}$  directly appear at the converter input terminals. Assuming the three-phase voltages to be balanced, the voltages to the input of the converter can be expressed as

$$v_{in}(t) = V_i \sin(\omega_i t + m_i)$$

(1)

where  $j \in \{a, b, c\}$  and  $m_a = 0$ ,  $m_b = -2\pi/3$ ,  $m_c = 2\pi/3$ . The peak of the input line to neutral voltage is defined as  $V_i$  and the frequency of the three-phase input voltages is  $\omega_i = 2\pi/T_i$ .

#### 2) Matrix Converter:

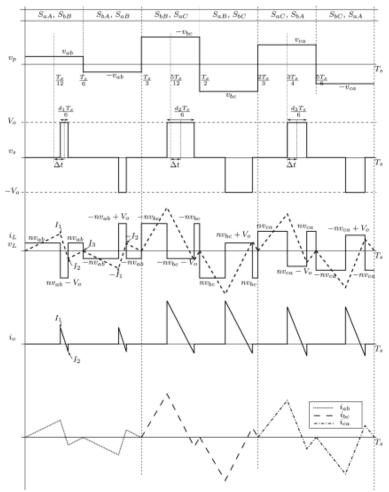

Fig. 3 shows typical primary voltage waveform  $v_p(v_{\rm AB}$ , over one switching cycle of period  $T_{\rm S}$  when  $(-(\pi/6) < \omega_i t < 0)$ . In this period,  $|v_{\rm bc}| > |v_{\rm ca}| > |v_{\rm ab}|$  and  $v_{\rm ab} > 0$ ,  $v_{\rm ca} > 0$ , and  $v_{\rm bc} < 0$ .  $T_{\rm S}$  is the switching period of the

MC. The period  $T_{\mathcal{S}}$  is divided into three equal times. The first third of the period alternates at 50% between a positive and negative value of the line-to-line voltage  $v_{ab}$ . Similarly, during the second third of  $T_{\mathcal{S}}$ , the primary voltage of the transformer alternates between negative and positive  $v_{bc}$  for equal time, and the primary voltage of the transformer alternates between positive and negative  $v_{ca}$  for equal time during the last third of  $T_{\mathcal{S}}$ . The voltages applied over a cycle of  $T_{\mathcal{S}}$  are given in the following equation:

$$v_p(t) = \begin{cases} |v_{ab}|, & 0 < t \le T_s/6 \\ -|v_{ab}|, & T_s/6 < t \le T_s/3 \\ |v_{bc}|, & T_s/3 < t \le T_s/2 \\ -|v_{bc}|, & T_s/2 < t \le 2T_s/3 \\ |v_{ca}|, & 2T_s/3 < t \le 5T_s/6 \\ -|v_{ca}|, & 5T_s/6 < t \le T_s. \end{cases}$$

(2)

Fig. 3. Typical waveforms over a switching cycle  $T_s(-(\pi/6) < \omega_i t < 0)$ .

#### 3) H-Bridge Modulation:

The H-bridge converter is comprised of switches  $[S_1-S_4]$  and produces a voltage  $(v_s$  in Fig. 2) pulse in each respective sixth of a cycle. The width of the pulse depends on current pair of input voltages being applied by the MC. In addition, these pulses are phase shifted with respect to  $v_p$ . The duty ratios of each third of the cycle of  $v_s$  are defined in (3)–(5) and depend on the voltage currently applied by the MC. The duty ratios are shown in Fig. 3. The first third of the cycle of the duty ratio is  $d_1(t)$ , the second third of the cycle of the duty ratio

is  $d_2(t)$ , and the final third of a cycle of the duty ratio is  $d_3(t)$ . These duty ratios are calculated using the measured line-to-line input voltages, the dc bus voltage, and the turns ratio. Given, the peak of the input line-line voltage  $\sqrt{3}V_i$ , the dc voltage  $V_o$ , the choice of the turns ratio should be such that the duty ratio never goes above one. The polarity of the generated pulses is same as the polarity of the applied voltage  $v_p$  of the MC

$$d_{1}(t) = \frac{n|v_{ab}(t)|}{V_{o}}$$

$$d_{2}(t) = \frac{n|v_{bc}(t)|}{V_{o}} (3)(4)(5)$$

$$d_{3}(t) = \frac{n|v_{ca}(t)|}{V_{o}}.$$

The time shift of the pulses produced by the H-bridge is denoted as  $\Delta t$  and is shown in Fig. 3. This modulation scheme imposes limits on the time shift. The pulse produced by the H-bridge will not be allowed to move outside of its respective one-sixth of the modulation cycle (referred as inner mode). This condition results in the following equation:

$$\frac{\frac{T_s}{12} + \Delta t + \frac{dT_s}{12} \le \frac{T_s}{6}}{\Delta t \le \frac{T_s}{12} - \frac{dT_s}{12}}.$$

(6)(7)

The phase shift  $\delta$  is defined in (8). The controllable range of the phase shift  $\delta$  is from -1 to 1

$$\delta = \frac{\Delta t}{T_s/12}$$

. (8)

The peak duty ratio of  $d_1(t)$ ,  $d_2(t)$ , and  $d_3(t)$  is defined in the following equation:

$$\hat{d} = \frac{\sqrt{3}nV_i}{V_0}.$$

(9)

The peak duty ratio is needed to determine the range of allowable phase shift. The range of allowable phase shift is found using (6)–(8) and (9) and is given in (10). Similar computation can be done for negative  $\delta$  as well

$$|\delta| \leq 1 - \overset{\wedge}{d}. (10)$$

View Source

Given the definition for phase shift  $\delta$ , duty ratios  $d_1,d_2,d_3$ , and the restriction on phase shift, the voltage applied by the H-bridge can be defined over the complete cycle of modulation of period Ts  $^1$

$$v_{s}(t)^{1} = \begin{cases} 0, & 0 < t \leq t_{a1} \\ V_{o}, & t_{a1} < t \leq t_{b1} \\ 0, & t_{b1} < t \leq T_{s}/6 + t_{a1} \\ -V_{o}, & T_{s}/6 + t_{a1} < t \leq T_{s}/6 + t_{b1} \\ 0, & T_{s}/6 + t_{b1} < t \leq T_{s}/3 + t_{a2} \\ V_{o}, & T_{s}/3 + t_{a2} < t \leq T_{s}/3 + t_{b2} \\ 0, & T_{s}/3 + t_{b2} < t \leq T_{s}/2 + t_{a2} \\ -V_{o}, & T_{s}/2 + t_{a2} < t \leq T_{s}/2 + t_{b2} \\ 0, & T_{s}/2 + t_{b2} < t \leq 2T_{s}/3 + t_{b3} \\ V_{o}, & 2T_{s}/3 + t_{b3} < t \leq 2T_{s}/3 + t_{b3} \\ 0, & 2T_{s}/6 + t_{a3} < t \leq 5T_{s}/6 + t_{b3} \\ 0, & 5T_{s}/6 + t_{b3} < t \leq T_{s}. \end{cases}$$

#### B. Computation of Input Current

In order to compute the average power and rms of the transformer winding currents over one period of the ac voltages  $[T_i=(1/f_i)]$ , we need to determine the inductor current  $i_L(t)$  over one modulation cycle of period  $T_s$ . As each third of the modulation cycle is identical, we will show the details of the computation of  $i_L$  over the first third of the modulation cycle when "ab" line-to-line voltage is applied at the transformer primary. The voltage across the inductor is given by obtained by taking the difference between the applied reflected primary voltage  $v_s(t)$  and the secondary voltage  $v_s(t)$

$$v_L(t) = nv_p(t) - v_s(t)$$

. (12)

Now, (12) can be used to compute the inductor current  $i_L(t)$

$$v_L(t) = L \frac{di_L}{dt}$$

. (13)

To compute  $i_L(t)$ , it is also assumed that, in steady state, the dc component of the inductor current is zero. This is true for a circuit with finite resistances where the dc offset will die down to zero under steady-state operation. As the applied secondary voltage pulse  $v_S(t)$ , in each one-sixth of the modulation cycle has a duty ratio of  $(n|v_p(t)|/V_o)$ , the average voltage applied across the inductor is zero. Therefore, it is possible to assume  $i_L(t)$  to be zero at the beginning of the modulation cycle. Let us focus on the determination of  $i_L(t)$  over the first one-sixth of the modulation cycle. As shown in Fig. 3,  $i_L(t)$  is a piecewise linear function of time, characterized by two peaks  $I_1$  and  $I_2$ . The expressions for  $I_1$  and  $I_2$  are given in (14) and (15), respectively.  $I_3=0$  because the average of the applied inductor voltage is zero over the period  $0 < t \le (T_S/6)$

$$I_{1} = \frac{n|v_{ab}|}{L} \frac{T_{s}}{12} (\delta - d + 1)$$

$$I_{2} = \frac{n|v_{ab}|}{L} \frac{T_{s}}{12} (\delta + d - 1).$$

(14)(15)

Following a similar procedure, it is possible to determine  $i_L(t)$  over one period of the modulation cycle. Note that the line-to-line current  $i_{ab}(t)$  is rectified in  $i_L(t)$  in the first one-third of the modulation cycle and zero in rest of the period as shown in Fig. 3. Therefore, the average value of  $i_{ab}$  over one modulation cycle is given in

$$\overline{i}_{ab} = \frac{2}{T_c} \int_0^{\frac{T_c}{6}} ni_L(\tau) d\tau = \frac{n^2 \delta}{36f_c} \sqrt{3} V_i \sin\left(\omega_i t + \frac{\pi}{6}\right)$$

(16)

where  $f_s = 1/T_s$ . Similarly, it is possible to compute the average value of the two other line currents as follows:

$$\bar{i}_{bc} = \frac{n^2 \delta}{36Lf_s} \sqrt{3} V_i \sin(\omega_i t - \frac{\pi}{2})$$

$$\bar{i}_{ca} = \frac{n^2 \delta}{36Lf_s} \sqrt{3} V_i \sin(\omega_i t + \frac{5\pi}{6}).$$

(17)(18)

It is possible to determine the line currents from the line-to-line currents using the following equation:

The resultant phase currents are given in the following equation:

$$\bar{i}_{a} = \frac{n^{2} \delta}{12 L f_{s}} V_{i} \sin (2\pi f_{i} t)$$

$$\bar{i}_{b} = \frac{n^{2} \delta}{12 L f_{s}} V_{i} \sin (2\pi f_{i} t - \frac{2\pi}{3}) (22)(23)(24)$$

$$\bar{i}_{c} = \frac{n^{2} \delta}{12 L f_{c}} V_{i} \sin (2\pi f_{i} t - \frac{4\pi}{3}).$$

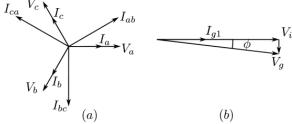

The magnitude of the three-phase currents is directly proportional to the control variable  $\delta$ . In addition, the modulation of the converter ensures that the fundamental component of the current is in phase with the line to neutral voltage. This ensures a displacement power factor of unity as shown in Fig. 4(a). However, due to a finite amount of switching ripple flowing to the grid, the power factor differs from unity. The relation between the displacement power factor and the power factor is given in [30] as

$$PF = \frac{1}{\sqrt{1 + THD^2}} DPF. (25)$$

Fig. 4. Phasor diagram showing (a) unity DPF and (b) effect of filter on power factor correction.

IEEE standards [31] specify the maximum amount of distortion in terms of the total harmonic distortion (THD). An upper limit of 5% is put on the allowable THD. Thus, the power factor of the system is very close to unity.

Ideally, the inductor  $L_{\rm ac}$  should appear as a short circuit at line frequency so that the grid voltage appears at the input of the ac-side converter. However, there is a finite drop across the leakage at fundamental frequency which prevents the converter from exact unity power factor operation. The modulation ensures that the voltage to the input of the converter  $V_i$  and fundamental grid current  $I_{g1}$  are in phase. However, due to filter drop, the current  $I_{g1}$  becomes leading with reference to the grid voltage for a power transfer from dc to ac [Fig. 4(b)]. However, this drop is very small and thus the converter operates at near unity power factor.

#### C. Design of Transformer Turns Ratio and Leakage Inductance

The average power (26) is found using (22)–(24) and (1)

$$P = \frac{1}{T_i} \int_0^{T_i} (v_a \bar{i}_a + v_b \bar{i}_b + v_c \bar{i}_c) dt = \frac{n^2 V_i^2}{8Lf_s} \delta = \frac{\hat{d}^2 V_0^2}{24Lf_s} \delta.$$

(26)

Note the average power is dc and linearly proportional to the control variable  $\delta$ . This simple relationship simplifies the control architecture. The design of the DAB converter is carried out keeping in mind the minimization of the losses and improvement of efficiency. Thus, the aim is to choose n and L such that the rms current is minimized for a given power transfer requirement. The rms current is computed using

$$i_{{\sf rms},L}^2 = \frac{1}{T_i} \int_0^{T_i} i_L^2(t) dt$$

. (27)

For evaluating the integral over line cycle, the rms current for one modulation cycle is computed first. Using the current magnitudes in (14) and (15), the rms current computed over first one-third of the modulation cycle is given by

$$i_{L,\text{rms1},Ts}^2 = \frac{T_s^2 d_1^2 V_o^2}{1296L^2} (d_1^2 - 2d_1 + 3\delta^2 + 1).$$

(28)

The rms currents in the subsequent two thirds of modulation cycle ( $i_{L,\mathrm{rms2,Ts}}^2$  &  $i_{L,\mathrm{rms3,Ts}}^2$ ) can be similarly obtained by replacing  $d_1$  by  $d_2$  and  $d_3$ , respectively. The net rms current in a switching cycle is  $i_{L,\mathrm{rms,Ts}}^2 = i_{L,\mathrm{rms2,Ts}}^2 + i_{L,\mathrm{rms2,Ts}}^2 + i_{L,\mathrm{rms3,Ts}}^2$ . Putting the values of  $d_1$ ,  $d_2$ , and  $d_3$  and taking the average over line cycle, the rms current is given by

$$i_{\text{rms,L}}^2 = \frac{T_s^2 \dot{d}^2 V_o^2}{10368\pi L^2} \left( 36\pi \delta^2 + 9\pi \dot{d}^2 - 64\dot{d} + 12\pi \right).$$

(29)

The average power in per unit is calculated with a power base of  $V_o^2/2\pi L f_s$

$$P_{pu} = \frac{\pi \delta \dot{d}^2}{12}. (30)$$

Similarly, the per-unit rms current using the base current  $I_{\rm base} = V_o/2\pi L f_s$  is given by

$$i_{\text{rmspu},L}^2 = \frac{\hat{\pi d^2}}{2592} \left( 36\pi\delta^2 + 9\pi\hat{d}^2 - 64\hat{d} + 12\pi \right).$$

(31)

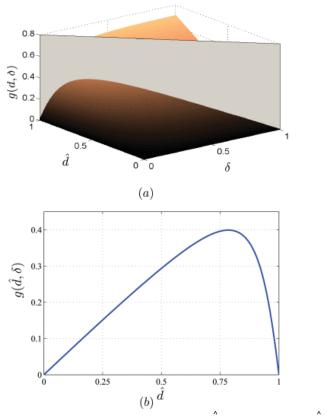

It can be seen that the per-unit power and rms currents depend on the design variables d and  $\delta$ . The objective is to choose d and  $\delta$  such that the net rms current is minimized for a given per-unit power transfer. Accordingly, the function  $g(d,\delta)=P_{\mathrm{pu}}/i_{\mathrm{rmspu},L}$  is plotted over the feasible range of d and d000 and d1010 and the maxima is identified. Apart from individual limits on d2100 and d3100 and d3100 should be chosen such that the converter operates in inner mode. For a positive d3000, we have

$$\overset{\wedge}{d} + \delta \leq 1.$$

(32)

Fig. 5. (a) Plot showing variation of  $g(d, \delta)$ . (b) Plot of  $g(d, \delta)$  for various d and  $\delta = 1 - d$ .

Since  $g(d,\delta)$  is a monotonically increasing function over d and  $\delta$ , it is easy to conclude that the optimum operating point occurs for  $d+\delta=1$ . This is identified as the contour generated because of intersection of the two curves in Fig. 5(b). The optimum value of d=0.76 is obtained from Fig. 5(b), which gives a maximum possible phase angle as  $\delta_{\rm max}=0.24$ . The per-unit maximum power under this operating condition is given by

$$P_{\text{pumax}} = \frac{\pi \delta \dot{d}^2}{12} = 0.036 pu.$$

(33)

Since the operating power P and the output voltage of the converter are known, the inductance can be accordingly designed so that the maximum per-unit power is achieved. The inductor L should be chosen such that

$$\frac{V_o^2}{2\pi f_S L} = \frac{P}{P_{\text{pumax}}}$$

(34)

The transformer turns ratio n is chosen using (9) once the operating d is fixed.

#### D. Soft-Switching

#### 1) ZCS of the AC-Side Bridge:

To ensure that the volt seconds applied from primary is balanced with the volt seconds applied from secondary in every one-sixth of the modulation cycle, pulsewidth of the secondary voltage is determined using (3)–(5). Ensuring a volt second balance will result in equal currents at the beginning and end of each one-sixth of modulation cycle. Every practical circuit will have some finite resistances. For a lossy circuit, the dc offset which

is governed by the complementary function of the solution will die down to zero, and the steady-state current will not have any dc offsets. It is possible to observe that the instants at which the ac-side converter switches, i.e., at t = 0,  $(T_s/6)$ ,  $(T_s/3)$ ,  $(T_s/2)$ ,  $(2T_s/3)$ ,  $(5T_s/6)$ , the primary winding current, which is reflected inductor current, is zero, so the primary converter is zero-current switched (ZCS). Note that, in practical implementation, due to magnetization component of the transformer current and voltage ripple at input and output, the primary current may not be zero, but would have a small magnitude at the time of switching.

#### 2) ZVS of the DC-Side Bridge:

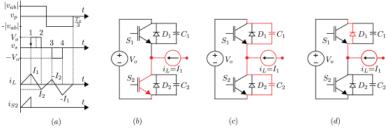

Fig. 6 shows a detailed diagram of a single leg of the dc-side H-bridge and the events occurring during switching. Fig. 6(a) shows the waveforms applied during first one-third of the modulation cycle. The H-bridge is switched four times during this interval. The first switching transition is considered where the switch  $S_2$  is turning off and switch  $S_1$  is turning on after dead time [Fig. 6(b)]. The inductor current  $i_L$  at this instant is  $I_1$  given by (15) and is assumed to be positive. Accordingly, the current is going into the pole terminal and switch  $S_2$  is conducting at the instant of turn off. Switch  $S_1$  was blocking a voltage of  $V_0$ . After switch turn off, the current has to flow through the capacitances. The current charges the capacitance  $C_2$  and discharges capacitance  $C_1$  [Fig. 6(c)]. The capacitances do not allow the voltage across the switch to change instantaneously but the channel current of switch  $S_2$  quickly goes to zero [32]. Thus, it is turned off at zero voltage switching (ZVS). Once, the capacitor  $C_1$  is completely discharged to zero [Fig. 6(d)], the current starts to flow through the diode  $D_1$ . If the switch  $S_1$  is turned on when its body diode is conducting, it is soft-switched.

Fig. 6. Soft-switching events. (a) Waveforms for one-third of line cycle. (b) Situation prior to device  $S_2$  turn off. (c) Switch  $S_2$  turned off: capacitor-assisted ZVS. (d) End of soft turn off of  $S_2$ , diode  $D_1$  conducting, soft turn on of  $S_1$ .

Thus, when leg 1 of the H-Bridge ( $S_1$  and  $S_2$ ) is switching, the inductor current  $i_L$  is  $I_1$  which should be *more than zero* to ensure soft-switching. Similarly, when leg 2 of the H-Bridge ( $S_3$  and  $S_4$ ) is switching, the inductor current  $i_L$  is  $I_2$  should be *less than zero* to ensure soft-switching. The currents in the next one-sixth of the modulation cycle follow the same pattern resulting in ZVS. It can be shown that the currents next two thirds of the modulation cycle follow the same pattern for a balanced operation. From (14) and (15), we have

$$(\delta - d_1 + 1) \ge 0$$

$(\delta + d_1 - 1) \le 0$ . (35)(36)

When  $\delta>0$ , since duty is a positive number <1, we have  $\delta\geq d_1-1$ , which gives  $(\delta-d_1+1)\geq 0$ . Also, since the converter is operating in inner mode,  $\delta\leq 1-d_1$  which gives  $(\delta+d_1-1)\leq 0$ . Same conclusions can be drawn for  $\delta<0$ .

Effect of Device Capacitances on Soft-Switching: The pole current  $i_L$  should be capable of charging/discharging the capacitances  $C_2$  and  $C_1$  within the dead time so that the transition is fully soft-switched. This imposes a minimum requirement on the pole current  $i_L$ . Assuming  $C_1 = C_2 = C$  and applying KCL in the pole circuit gives

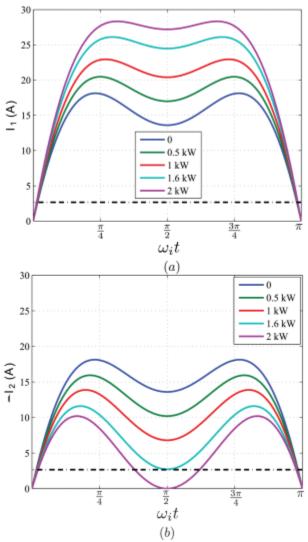

$$i_L = 2C \frac{dv_{c2}}{dt}. (37)$$

Noting that the time of charging the capacitor fully should be less than the dead time of the circuit we have,  $I_{L\min}=(2CV_o/t_{\rm dead})$  [33]. The variations of  $I_1$  and  $-I_2$  over line cycle for various loads are plotted in Fig. 7(a) and (b), respectively. The minimum current required for complete soft-switching (C=2nF,  $t_{\rm dead}=600$ ns) is also shown in the figures. It can be observed that for  $\omega_i t$  close to 0 and  $\pi$ , ZVS may not happen in both the legs. This range remains relatively unchanged with loading. ZVS may not happen in one of the legs for a narrow region around  $\omega_i t = \pi/2$  for heavy loading conditions. However, Fig. 7(b) reveals that this range is very small. As  $\delta$  is increased, the magnitude of current  $I_1$  increases and magnitude of current  $I_2$  decreases as shown in Fig. 7(a) and (b), respectively. This improves the soft-switching range of one leg in the H-bridge but reduces the soft-switching range of other leg. The converter soft-switching is unaffected under light loading conditions, whereas the range reduces for high loading of the converter.

Fig. 7. Variation over line cycle. (a)  $I_1$  for various load. (b)  $-I_2$  for various load.

At the instant of switching, the pole current  $i_L$  is modeled as a current source. This is true only if we have enough series inductance L. This inductance is a series combination of the leakage inductance of the transformer and the external inductance added to achieve the power transfer. It is possible to show that L must satisfy the following inequality:

$$\frac{2CV_o}{i_I} < \sqrt{2LC}.$$

(38)

#### E. Design of Filter

#### 1) Design of DC-Side Filter:

The instantaneous output current is governed by the switching function of the secondary bridge and the inductor current,  $i_L$

$$i_{\text{out}} = (S_1 - S_3)i_L$$

. (39)

The output rms current is computed using the following equation:

$$i_{\text{rms},o}^{2} = \frac{1}{T_{i}} \int_{0}^{T_{i}} i_{\text{out}}^{2} dt$$

$$i_{\text{rms},o}^{2} = \frac{T_{s}^{2} d^{3} V_{o}^{2}}{25920\pi L^{2}} (240\delta^{2} + 64d^{2} - 45\pi d + 80).$$

(40)(41)

The per-unit average current  $i_{\text{avpu}}$  is computed using (30), which can be multiplied with base current to obtain the actual current. The filter needs to be designed such that the entire switching frequency ripple flows through it. The rms ripple current is given by

$$i\tilde{i}_{\text{rms}} = \sqrt{i_{\text{rms},o}^2 - i_{\text{av}}^2}$$

. (42)

The operating point of the converter decides the value of the rms and average current. Once the ripple current rms is determined, it is assumed that the entire ripple is concentrated at the switching frequency. This results in a slight overdesign [34]. Considering an allowable voltage ripple to be a  $\lambda$  fraction of the dc voltage  $V_o$ , the filter admittance is given by

$$Y_{\rm pu} = \omega_s C_{\rm dc} = \frac{\tilde{i}_{\rm rms}}{\lambda V_o}$$

. (43)

Although the capacitor  $C_{

m dc}$  is designed to carry the entire ripple at switching frequency, some part of it may leak into the dc source. To prevent this, an inductor  $L_{

m dc}$ , is put in series with the voltage source  $V_o$ . The inductor is designed such that only 5% of the total ripple flows into the source. Thus, the output current  $i_o(\omega_s)$  is

$$\tilde{i}_{o}(\omega_{s}) = \frac{1}{|-L_{dc}C_{dc}\omega_{s}^{2}+1|} \le 0.05 \tilde{i}_{rms}.$$

(44)

#### 2) Design of AC-Side Filter:

The instantaneous input current is given by the primary current  $ni_L$  and the switching function of the primary bridge. The instantaneous current in phase A is given by

$$i_a = (S_{aA} - S_{aB})ni_L$$

. (45)

Using (45), the rms current in phase A is given by

$$i_{\text{rms,a}}^{2} = \frac{\frac{1}{T_{i}} \int_{0}^{T_{i}} i_{a}^{2} dt}{i_{\text{rms,a}}^{2}} i_{\text{rms,a}}^{2} = \frac{\frac{7}{S} d^{2} V_{o}^{2} n^{2}}{15552\pi L^{2}} \left(36\pi \delta^{2} + 9\pi d^{2} - 64d + 12\pi\right).$$

(46)(47)

The capacitive filter  $C_{\rm ac}$  should be designed to carry the entire ripple component of the current. The ripple current rms  $\tilde{i}_{{\rm rms},a}$  is found by subtracting the fundamental current rms from  $i_{{\rm rms},a}$  in (47). It is assumed that the

entire ripple is concentrated at the switching frequency. Considering an allowable voltage ripple to be a  $\lambda$  fraction of the ac voltage  $V_i$ , the filter admittance is given by

$$Y_{pu} = \omega_s C_{ac} = \frac{\tilde{i}_{rms,a}}{\lambda V_i}$$

. (48)

An inductor  $L_{\rm ac}$  needs to be put after the capacitive filter to prevent any high frequency current from flowing into the grid. Following the IEEE THD requirement of 5% [31], the ripple current  $\overset{\sim}{i_g}$  should be limited to 5% of fundamental

$$\tilde{i}_{g}(\omega_{s}) = \frac{1}{|-L_{ac}C_{ac}\omega_{s}^{2}+1|} \le 0.05\tilde{i}_{arms}.$$

(49)

## **SECTION III. Simulation and Experimental Results**

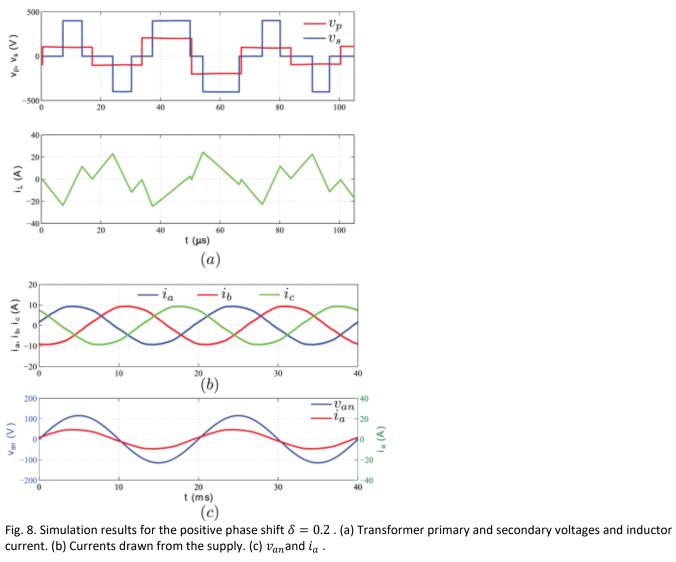

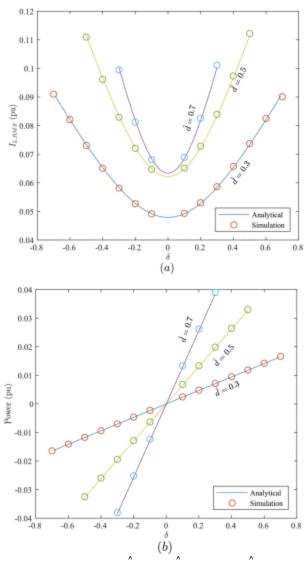

The proposed modulation strategy was simulated with MATLAB/Simulink and the results have been presented in Fig. 8. The simulation parameters are listed in Table I. Fig. 8(a) shows the transformer primary and secondary voltages, and the inductor current for a switching period for  $\delta=0.2$ . It can be observed that the inductor current is close to zero at the transitions of  $v_p$ , demonstrating ZCS in the primary side converter, while the inductor current polarities at switching transitions in  $v_s$  shows that ZVS occurs in the secondary side H-bridge. Both the ac and dc-side currents have high-frequency harmonics starting at switching frequency. The input ac currents for all three phases are shown in Fig. 8(b). The currents are sinusoidal and balanced as predicted by (22)–(24). The phase A voltage  $v_{an}$  and the current  $i_a$  are nearly in phase in Fig. 8(c), confirming unity power factor operation. Similar observations were found from the simulation results for negative phase shift with  $\delta=-0.2$ . Finally, in order to demonstrate the accuracy of the analysis done for power transfer and rms currents, the system was simulated for different modulation indices and phase shift values and the simulation results have been plotted together with analytical values in Fig. 9. It is observed that the simulation results follow the analytical values closely.

**TABLE I Simulation and Experimental Parameters**

| L                   | n   | $V_i$ | $V_o$ | $f_i$ | $f_s$ | P     |

|---------------------|-----|-------|-------|-------|-------|-------|

| $47 \mu \mathrm{H}$ | 1.5 | 115V  | 400V  | 50Hz  | 10kHz | 1.6kW |

Fig. 9. Comparison for d=0.3, d=0.5, and d=0.7. (a) Comparison of analytical and simulated per-unit rms currents. (b) Comparison of analytical and simulated dc per-unit power.

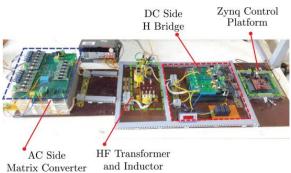

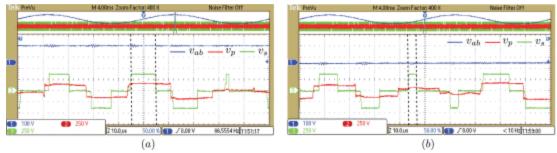

The setup used for the experiment is shown in Fig. 10. The list of components is given in Table II. The experimental setup was run with the parameters listed in Table I with  $\delta=\pm0.2$ . A positive  $\delta$  signifies ac–dc power flow and viceversa. The leakage inductance current  $(i_L)$ , primary voltage  $(v_p)$ , and secondary voltage  $(v_s)$  for positive  $\delta$  are shown in Fig. 11(a). Note that for each time the primary voltage switches, the current is essentially close to zero, which confirms zero-current switching of the MC. The sign of the inductor current at the transitions of secondary voltage  $v_s$  ensures the soft-switching of the dc-side H-bridge. The switching cycle waveforms for negative  $\delta$  are shown in Fig. 11(b). Again, it is possible to observe each time the MC voltage changes, the current through the leakage inductance is essentially close to zero.

#### **TABLE II Component List**

| Part                    | Part Number      | Rating             |

|-------------------------|------------------|--------------------|

| IGBTs $S_{aA} - S_{cB}$ | IKW40N120H3      | 1200V 40A          |

| IGBTs $S_1 - S_4$       | SKM100GB12T4     | 1200V 100A         |

| Capacitor $C_{ac}$      | C4ATJBW5150A3NJ  | $15\mu F \times 2$ |

| Capacitor $C_{dc}$      | MKP1848C61012JP4 | $10\mu F \times 2$ |

Fig. 10. Experimental Setup.

Fig. 11. Modulation cycle waveforms for (a)  $\delta=0.2$  and (b)  $\delta=-0.2$  .

Since the H-bridge is duty cycle modulated, the pulsewidth of the voltage applied at the secondary depends on phase of the input line voltage. This is demonstrated in Fig. 12. For a modulation cycle where the line voltage  $v_{ab}$  is close to its peak value [Fig. 12(a)], the pulsewidth of the applied secondary voltage is maximum. Similarly, a modulation cycle where the  $v_{ab}$  is close to zero [Fig. 12(b)], the pulsewidth of the applied secondary voltage is small.

Fig. 12. Experimental results showing duty cycle modulation. (a) Line voltage  $v_{ab}$  close to peak value. (b) Line voltage  $v_{ab}$  close to zero crossing.

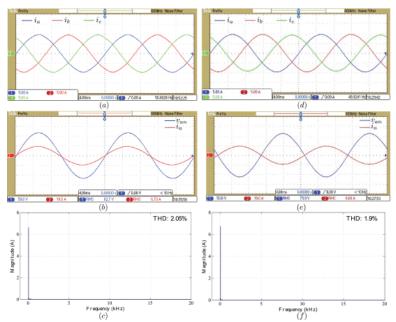

The three-phase filtered input currents for  $\delta=0.2$  and  $\delta=-0.2$  are shown in Fig. 13(a) and (d), respectively. These waveforms confirm balanced three-phase operation for both ac–dc and dc–ac operations of the converter. Fig. 13(b) shows the line-neutral voltage  $v_{an}$  and the line current  $i_a$  for ac–dc operation. The current is in phase with the voltage indicating unity power factor operation. Fig. 13(e) shows the same result for dc–ac operation. The current  $i_a$  is 180° out of phase with voltage indicating negative power flow. The grid current is free from any considerable high-frequency components for both the cases indicating proper filtering. The experimentally obtained harmonic spectra of the current are shown in Fig. 13(c) and (f). The THD for both the cases is within the IEEE requirement. A comparison between the theoretical, simulation, and experimental quantities is shown in Table III. A good agreement can be observed.

TABLE III Comparison at  $\delta$ =0.2

| $\delta = 0.2$ | Input Power (W) | AC Current (A) | PF   |

|----------------|-----------------|----------------|------|

| Theory         | 1631            | 6.66           | 0.99 |

| Simulation     | 1625            | 6.71           | 0.98 |

| Experiment     | 1662            | 6.70           | 0.99 |

Fig. 13. Line cycle waveforms at a power level of 1.6 kW. (a) Three-phase currents ( $\delta=0.2$ ). (b) unity power factor (UPF) operation ( $\delta=0.2$ ). (c) Experimental THD ( $\delta=0.2$ .) (d) Three-phase currents ( $\delta=-0.2$ ). (e) UPF operation ( $\delta=-0.2$ ). (f) Experimental THD ( $\delta=-0.2$ ).

#### A. Efficiency and Loss Estimation

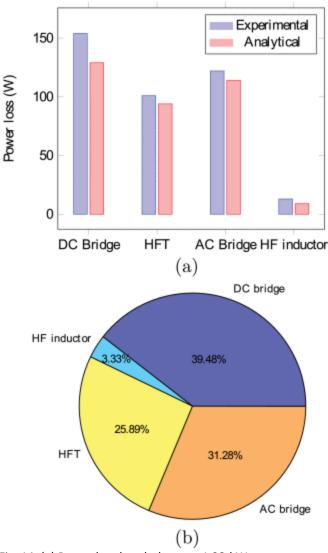

The experimentally obtained efficiency and power factor are shown in Table IV. The main reason for low efficiencies is that the hardware is not specifically designed for the operating power level but to only test the validity of the proposed modulation strategy. A theoretical and experimental loss breakdown is carried out for further insight. The conduction losses in primary and secondary bridges and the total losses in the transformer and high-frequency inductor are calculated. Since the current waveform in each modulation cycle has different slopes, it is difficult to arrive at an analytical closed-form expression for conduction loss. The conduction loss for primary and secondary bridges has been obtained numerically. The transformer and inductor copper loss is computed using the rms current and the winding resistances

$$P_{\text{cu,HFT}} = I_{\text{rms},p}^2 R_p + I_{\text{rms},s}^2 R_s. (50)$$

A comparison between the analytically and the experimentally obtained losses is given in Fig. 14(a). A good agreement is observed. Fig. 14(b) shows the percentage loss distribution in each stage of the converter. It can be seen that major losses are the conduction losses in the bridges and copper loses in the transformer. For analytical demonstration of soft-switching, the switching losses are calculated assuming the turn off to be completely hard-switched. The total losses obtained are 242W. However, the experimentally obtained losses are much less than this value 154 W, which provide an analytical evidence of soft-switching.

TABLE IV Experimental Efficiency and Power Factor

| AC Power (W)   | 1572 | 1191 | 825  | -1639.8 | -1380 | -1035 |

|----------------|------|------|------|---------|-------|-------|

| Efficiency (%) | 82.1 | 81.6 | 80.8 | 81.2    | 78.0  | 76.3  |

| Power Factor   | 0.99 | 0.98 | 0.97 | 0.99    | 0.99  | 0.99  |

Fig. 14. (a) Power loss break-down at 1.38-kW output power obtained experimentally and analytically. (b) Percentage loss distribution shown at 1.38-kW output power obtained experimentally.

#### B. Experimental Verification of ZVS in H-Bridge

Fig. 15(a) shows the waveforms during turn off of switch  $S_1$  and turn on of  $S_2$  after dead time (refer Fig. 2). The switch  $S_1$  was carrying a current  $i_L < 0$  as shown in Fig. 15(a). At time  $t_0$ , the voltage input to the gate-emitter circuit is reduced to -15 V. The gate-emitter voltage starts to reduce. Since the sum of voltage across the switch and the diode is constant, the diode cannot start conducting unless it has become forward biased, or equivalently the voltage across the switch (and  $C_1$ ) has risen to  $V_0$ . The constant pole current  $i_L$  is the sum of currents through the diode, switch, and their respective capacitances. Since the pole current is no longer restricted to the switch channel, the current transfers to the capacitors  $C_1$  and  $C_2$ . The voltage rise across switch  $S_1$  starts at  $t=t_1$  after the gate-emitter voltage goes below the threshold ( $v_{\rm ge}(t_1)=2V< V_{\rm ge,th}=5.8V$ ). The switch is in cutoff region for t>t1, so the channel current must be zero. Thus, the current through the switch has become zero before voltage starts increasing implying ZVS turn off of  $S_1$  [32]. The negative value of inductor current  $i_L$  discharges the capacitance  $C_2$  and charges capacitor  $C_1$ . This can be seen in Fig. 15(b). At time  $t_2$ , the capacitor  $C_1$  is charged to  $V_0$  and the diode  $D_2$  starts to conduct. This makes the voltage across switch  $S_2$  zero. At  $t_3$ , the switch  $S_2$  is turned on with zero  $v_{ce}$ . This ensures ZVS turn on of  $S_2$ . Similar transitions can be observed for switching events in the other leg which verify the occurrence of soft-switching in the bridge.

Fig. 15. Experimental waveforms demonstrating soft-switching. (a) Waveforms demonstrating soft turn off. (b) Waveforms demonstrating soft turn on.

#### **SECTION IV. Conclusion**

In this paper, a modulation scheme for a single-stage three-phase ac–dc bidirectional converter with high-frequency link is presented. The main features of the modulation scheme are single-stage power conversion, bidirectional power flow, open-loop power factor correction, soft-switching of primary and secondary side power converters, and simple linear relationship between the control variable  $\delta$  and the transferred dc power. Presented analysis of the proposed scheme shows that all these benefits are achieved. These features are successfully demonstrated and validated through presented simulations and experimental results. The performance of the proposed topology was investigated to be at par with the conventional two-stage topology. Due to loss-less switching, the switching frequency of the converter may be increased leading to high power density. Moreover, due to bidirectional power flow capability, high power density and loss-less switching, the proposed solution may find promising solution for V2G application.

# **Appendix**

# SECTION A. Comparison With Conventional Two Stage Topology

A detailed comparison of the proposed topology and the multistage topology shown in Fig. 1(a) is carried out. Same power (P), input ( $V_i$ ), and output ( $V_o$ ) voltage levels are assumed for both the topologies. The multistage topology used for comparison consists of a dc–dc DAB operated with conventional phase shift modulation followed by a three-phase pulsewidth modulation (PWM) rectifier realized with a voltage source inverter modulated using conventional space vector PWM. The DAB converter is modulated at a point where power is maximum and the VSI is modulated with the maximum possible modulation index. For comparing cost and power density, the device requirement (number, voltage, current rating) and transformer size are compared in Table V. For comparing the efficiency, a loss comparison is given in Table VI. It can be seen from Table V that most of the parameters are comparable for both the topologies. However, Table VI reveals that the proposed topology is having higher conduction losses. However, the switching losses for the proposed converter are absent, which enables operation of the converter at much higher switching frequency leading to better size and power density.

#### **TABLE V Topology Comparison**

|                   |                        | Scaling Factor       | VSI+DAB (square wave)    | Proposed topology |

|-------------------|------------------------|----------------------|--------------------------|-------------------|

| AC side converter | No. of switches        | -                    | 10                       | 12                |

|                   | Blocking voltage       | $V_i$                | $\sqrt{3}$               | $\sqrt{3}$        |

|                   | Switch RMS current     | $P/V_i$              | 0.333 (VSI), 0.667 (DAB) | 0.6373 (Switch)   |

| DC side converter | No. of switches        | -                    | 4                        | 4                 |

|                   | Blocking voltage       | $V_o$                | 1                        | 1                 |

|                   | Switch RMS current     | $P/V_o$              | 1.155                    | 1.0264, 2.2968    |

|                   | Electrolytic capacitor | -                    | 1                        | 0                 |

| Transformer       | Area Product           | $P/(f_sJB_{max}K_w)$ | 0.272                    | 0.3189            |

| Inductor          | Value                  | $V_o^2/(2\pi f_s)$   | 0.267                    | 0.036             |

|                   | RMS Current            | $P/V_o$              | 1.633                    | 2.5157            |

J: Current density, Bmax: Peak flux density, Kw: Window Factor

#### **TABLE VI Loss Comparison**

|                   |                 | Scaling Factor                            | VSI+DAB (square wave) | Proposed topology |

|-------------------|-----------------|-------------------------------------------|-----------------------|-------------------|

| AC side converter | Conduction loss | $\left(\frac{P}{V_i}\right)^2 R_{ON,pr}$  | 2.447                 | 4.8738            |

|                   | Switching loss  | $Pf_st_{sw,pr}$                           | 1.104                 | 0                 |

| DC side converter | Conduction loss | $\left(\frac{P}{V_o}\right)^2 R_{ON,sec}$ | 5.336                 | 12.6575           |

|                   | Switching loss  | $Pf_st_{sw,sec}$                          | 0                     | 0                 |

| Transformer       | Core & Cond.    | K                                         | 0.376                 | 0.424             |

Losses Proportional to  $(A_c A_w)^{0.75}$ , K being the constant of proportionality factor  $R_{ON,pr}$  and  $R_{ON,sec}$  are device resistances.  $t_{sw,sec}$ : Device Switching Time

#### References

- **1.** A. Emadi, Y. J. Lee, K. Rajashekara, "Power electronics and motor drives in electric hybrid electric and plug-in hybrid electric vehicles", *IEEE Trans. Ind. Electron.*, vol. 55, no. 6, pp. 2237-2245, Jun. 2008.

- **2.** P. He, A. Khaligh, "Comprehensive analyses and comparison of 1 kW isolated DC–DC converters for bidirectional EV charging systems", *IEEE Trans. Transp. Electrific.*, vol. 3, no. 1, pp. 147-156, Mar. 2017.

- **3.** B.-K. Lee, J.-P. Kim, S.-G. Kim, J.-Y. Lee, "An isolated/bidirectional PWM resonant converter for V2G(H) EV onboard charger", *IEEE Trans. Veh. Technol.*, vol. 66, no. 9, pp. 7741-7750, Sep. 2017.

- **4.** S. Inoue, H. Akagi, "A bidirectional DC–DC converter for an energy storage system with galvanic isolation", *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2299-2306, Nov. 2007.

- **5.** N. H. Baars, H. Huisman, J. L. Duarte, J. Verschoor, "A 80 kW isolated DC-DC converter for railway applications", *Proc. 16th Eur. Conf. Power Electron. Appl.*, pp. 1-10, Aug. 2014.

- **6.** M. Kwon, S. Choi, "An electrolytic capacitorless bidirectional EV charger for V2G and V2H applications", *IEEE Trans. Power Electron.*, vol. 32, no. 9, pp. 6792-6799, Sep. 2017.

- **7.** U. R. Prasanna, A. K. Singh, K. Rajashekara, "Novel bidirectional single-phase single-stage isolated AC–DC converter with PFC for charging of electric vehicles", *IEEE Trans. Transp. Electrific.*, vol. 3, no. 3, pp. 536-544, Sep. 2017.

- **8.** S. Li, J. Deng, C. C. Mi, "Single-stage resonant battery charger with inherent power factor correction for electric vehicles", *IEEE Trans. Veh. Technol.*, vol. 62, no. 9, pp. 4336-4344, Nov. 2013.

- **9.** D. Patil, V. Agarwal, "Compact onboard single-phase EV battery charger with novel low-frequency ripple compensator and optimum filter design", *IEEE Trans. Veh. Technol.*, vol. 65, no. 4, pp. 1948-1956, Apr. 2016.

- 10. M. N. Kheraluwala, R. W. Gascoigne, D. M. Divan, E. D. Baumann, "Performance characterization of a high-power dual active bridge DC-to-DC converter", *IEEE Trans. Ind. Appl.*, vol. 28, no. 6, pp. 1294-1301, Nov./Dec. 1992.

- **11.** F. Krismer, J. W. Kolar, "Efficiency-optimized high-current dual active bridge converter for automotive applications", *IEEE Trans. Ind. Electron.*, vol. 59, no. 7, pp. 2745-2760, Jul. 2012.

- **12.** H. van Hoek, M. Neubert, R. W. D. Doncker, "Enhanced modulation strategy for a three-phase dual active bridge—Boosting efficiency of an electric vehicle converter", *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5499-5507, Dec. 2013.

- **13.** A. K. Jain, R. Ayyanar, "PWM control of dual active bridge: Comprehensive analysis and experimental verification", *IEEE Trans. Power Electron.*, vol. 26, no. 4, pp. 1215-1227, Apr. 2011.

- **14.** F. Krismer, J. W. Kolar, "Closed form solution for minimum conduction loss modulation of DAB converters", *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 174-188, Jan. 2012.

- **15.** G. G. Oggier, G. O. García, A. Oliva, "Switching control strategy to minimize dual active bridge converter losses", *IEEE Trans. Power Electron.*, vol. 24, no. 7, pp. 1826-1838, Jul. 2009.

- **16.** A. Tong, L. Hang, G. Li, X. Jiang, S. Gao, "Modeling and analysis of a dual-active-bridge-isolated bidirectional DC/DC converter to minimize RMS current with whole operating range", *IEEE Trans. Power Electron.*, vol. 33, no. 6, pp. 5302-5316, Jun. 2017.

- **17.** H. Bai, C. Mi, "Eliminate reactive power and increase system efficiency of isolated bidirectional dual-active-bridge DC–DC converters using novel dual-phase-shift control", *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 2905-2914, Nov. 2008.

- **18.** B. Zhao, Q. Song, W. Liu, G. Liu, Y. Zhao, "Universal high-frequency-link characterization and practical fundamental-optimal strategy for dual-active-bridge DC-DC converter under PWM plus phase-shift control", *IEEE Trans. Power Electron.*, vol. 30, no. 12, pp. 6488-6494, Dec. 2015.

- **19.** H. Shi, H. Wen, J. Chen, Y. Hu, L. Jiang, G. Chen, "Minimum-reactive-power scheme of dual-active-bridge DC–DC converter with three-level modulated phase-shift control", *IEEE Trans. Ind. Appl.*, vol. 53, no. 6, pp. 5573-5586, Nov./Dec. 2017.

- **20.** K. Vangen, T. Melaa, A. K. Adnanes, "Soft-switched high-frequency high power DC/AC converter with IGBT", *Proc. 23rd Annu. IEEE Power Electron. Spec. Conf.*, vol. 1, pp. 26-33, Jun./Jul. 1992.

- **21.** N. D. Weise, G. Castelino, K. Basu, N. Mohan, "A single-stage dual-active-bridge-based soft switched AC–DC converter with open-loop power factor correction and other advanced features", *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4007-4016, Aug. 2014.

- **22.** R. Baranwal, G. F. Castelino, K. Iyer, K. Basu, N. Mohan, "A dual-active-bridge-based single-phase AC to DC power electronic transformer with advanced features", *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 313-331, Jan. 2018.

- **23.** F. Jauch, J. Biela, "Combined phase-shift and frequency modulation of a dual-active-bridge AC–DC converter with PFC", *IEEE Trans. Power Electron.*, vol. 31, no. 12, pp. 8387-8397, Dec. 2016.

- **24.** J. Everts, F. Krismer, J. Van den Keybus, J. Driesen, J. W. Kolar, "Optimal ZVS modulation of single-phase single-stage bidirectional dab AC–DC converters", *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 3954-3970, Aug. 2014.

- **25.** A. K. Singh, P. Das, S. K. Panda, "A novel matrix based isolated three phase AC-DC converter with reduced switching losses", *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, pp. 1875-1880, Mar. 2015.

- **26.** R. Baranwal, K. V. Iyer, K. Basu, G. F. Castelino, N. Mohan, "A reduced switch count single-stage three-phase bidirectional rectifier with high-frequency isolation", *IEEE Trans. Power Electron.*, vol. 33, no. 11, pp. 9520-9541, Nov. 2018.

- **27.** M. A. Sayed, K. Suzuki, T. Takeshita, W. Kitagawa, "Soft-switching PWM technique for grid-tie isolated bidirectional DC–AC converter with SiC device", *IEEE Trans. Ind. Appl.*, vol. 53, no. 6, pp. 5602-5614, Nov./Dec. 2017.

- **28.** D. Varajão, R. E. Araújo, L. M. Miranda, J. A. P. Lopes, "Modulation strategy for a single-stage bidirectional and isolated AC–DC matrix converter for energy storage systems", *IEEE Trans. Ind. Electron.*, vol. 65, no. 4, pp. 3458-3468, Apr. 2018.

- **29.** N. D. Weise, K. Basu, N. Mohan, "Advanced modulation strategy for a three-phase AC-DC dual active bridge for V2G", *Proc. IEEE Vehicle Power Propuls. Conf.*, pp. 1-6, Sep. 2011.

- **30.** N. Mohan, T. M. Undeland, Power Electronics: Converters Applications and Design, Hoboken, NJ, USA:Wiley, 2007.

- **31.** IEEE, 1547.2-2008, "IEEE Standard for Interconnecting Distributed Resources With Electric Power Systems", pp. 1-207, 2009.

- **32.** M. Trivedi, K. Shenai, "Modeling the turn-off of IGBT's in hard-and soft-switching applications", *IEEE Trans. Electron Devices*, vol. 44, no. 5, pp. 887-893, May 1997.

- **33.** N. Mohan, Power Electronics: A First Course, Hoboken, NJ, USA:Wiley, 2011.

- **34.** K. Basu, A. K. Sahoo, V. Chandrasekaran, N. Mohan, "Grid-side AC line filter design of a current source rectifier with analytical estimation of input current ripple", *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6394-6405, Dec. 2014.